# Master Thesis & Internship Projects @ imec

# 2017 Topic Guide

|   | CMOS & beyond CMOS                                                                                                                                 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | 3D interconnect-based segmented bus architecture modelling and exploration                                                                         |

| ( | Organic polymers for microbumps passivation                                                                                                        |

| S | Sub-nano engineered magnetic tunnel junction stacks for STT-MRAM applications                                                                      |

| S | Study of the kinetics of chemical reactions in nanostructures                                                                                      |

|   | Novel spin-on method to deposit self-assembled monolayers and thin polymeric films for surface and<br>nterface engineering in nano-IC applications |

| 1 | Machine learning based computational lithography                                                                                                   |

|   | The giant Voltage Control of Magnetic Anisotropy (VCMA) effect for enabling next generation spintron<br>and magnetic memories                      |

|   | n-situ electron beam study of fracture events to assess the strength and compliance of advanced BEOL<br>structures at the nanoscale                |

| F | Full-zone band structure calibration for the quantum mechanical simulation of confined III-V TFETs                                                 |

|   | Surface chemistry and atomic layer etching of III-V semiconductors for 5 nanometer CMOS technologie<br>and beyond                                  |

| E | Edge placement error budgeting in CMOS process flow                                                                                                |

| ŀ | Automatic recipe and data management development for Fab automation                                                                                |

| ( | Computational methods to assess the mechanical properties of thin films                                                                            |

| ŀ | Atomic layer deposition of metal doped HfO2 as ferroelectric material for future memory technologies                                               |

| ŀ | Advanced Source-Drain contact resistance                                                                                                           |

| 3 | 3D chemical analysis of microelectronics systems                                                                                                   |

| ŀ | Atom Probe Tomography for future 3D metrology applications                                                                                         |

| S | Seeding and growth of boron-doped diamond thin films                                                                                               |

| E | Electrical SPM for the analysis of magnetic memory                                                                                                 |

| ŀ | Advanced analysis of Rutherford backscattering spectrometry through parallel processing                                                            |

| E | Embedded distributed human-machine application for accelerator based metrology                                                                     |

| ( | One-dimensional carrier profiling of blanket and confined semiconducting structures                                                                |

| ( | Composition measurements in advanced III-V nanostructures using Raman spectroscopy                                                                 |

| ٦ | Transmission electron microscopy: more than an image                                                                                               |

| 1 | Metal deposition for future technology nodes                                                                                                       |

| F | Pt-group metal nanowires for advanced interconnects                                                                                                |

| S | Simulations and design of spin wave based logic devices                                                                                            |

| 1 | Modeling of magnetoelectric coupling for advanced spintronic applications                                                                          |

| F | Physical mechanisms for the detection of magnetization textures for novel spintronic devices                                                       |

| ŀ | Area selective deposition – bottom up strategies for patterning                                                                                    |

|      | Impact of higher order precursors on epitaxial growth of SiGeSn alloys                                                          | 28   |

|------|---------------------------------------------------------------------------------------------------------------------------------|------|

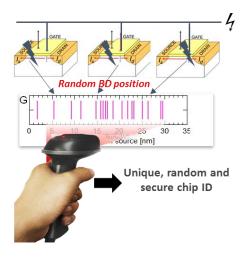

|      | Design and characterization of reliable Physically Unclonable Functions in CMOS                                                 | 29   |

|      | Spin wave devices for beyond CMOS applications                                                                                  |      |

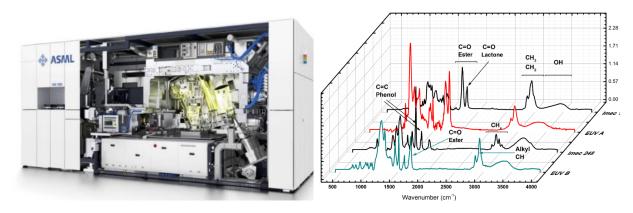

|      | Characterization of photoresist for EUV lithography                                                                             | 31   |

|      | Digital design of flexible deep learning kernels                                                                                | 32   |

|      | Algorithmic formulation of Hierarchical Temporal Memories                                                                       | 32   |

|      | Characterization and understanding of semiconductor materials for advanced CMOS                                                 | 33   |

|      | Optical characterization of 2D semiconductors                                                                                   | 34   |

|      | Magnetic domain wall injector                                                                                                   | 34   |

|      | Spintronic memristor                                                                                                            | 35   |

|      | Surface and interface engineering of 2D semiconductors and their applications for electronics                                   | 35   |

|      | Emergent electromagnetic fields and Topological Hall Effect for magnetic skyrmions                                              | 36   |

|      | Defect reduction in directed self-assembly processes                                                                            | 36   |

|      | LSTM architecture implementation using binarized neural network                                                                 | 37   |

|      | III-V gatestacks: Investigation into defect reduction                                                                           | 38   |

|      | ESD reliability of high mobility finFET devices for ultimate CMOS                                                               | 39   |

|      | Assessment of the FeFET capabilities as synaptic node in neuromorphic computation                                               | 39   |

|      | Doppler profilometry                                                                                                            | 40   |

|      | Comparison of Strained SiGe epitaxial growth on Si vs SiGe SRBs in view of advanced MOS devices                                 | 41   |

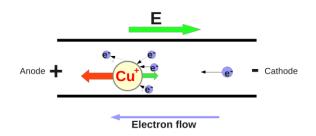

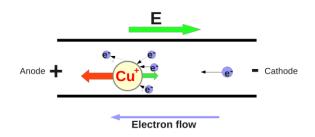

|      | Study of electromigration mechanisms in advanced nanoelectronics interconnects by means of low-<br>frequency noise measurements | 41   |

|      | Development of a new electromigration test method for advanced nanoelectronics interconnects                                    | 43   |

| II.  | Image Sensors and Vision Systems                                                                                                | . 45 |

|      | High speed column ADC for CMOS Image sensors                                                                                    | 45   |

|      | Highly efficient row drivers for TDI Image sensors                                                                              |      |

|      | Readout electronics for ultra high-speed imaging                                                                                |      |

|      | Readout electronics for single photon imaging                                                                                   | 46   |

|      | Thin film-based image sensors                                                                                                   | 46   |

| III. | . Silicon Photonics                                                                                                             | . 48 |

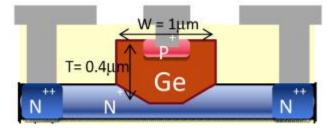

|      | Ge(Si) multi quantum well based optoelectronic devices                                                                          | 48   |

|      | Characterization of graphene photonics devices                                                                                  | 48   |

|      | Process development and characterization of devices based on ferroelectric oxides for silicon photonics applications            |      |

|      | Reliability behavior of Germanium waveguide photodetectors                                                                      |      |

|      | Development of a parallel test method for wafer-level characterisation of silicon photonics devices                             |      |

| IV. | Thin-Film Flexible Electronics                                                                       | 52 |

|-----|------------------------------------------------------------------------------------------------------|----|

|     | Optical design of infrared thin-film photodetectors                                                  | 52 |

|     | Organic patterning                                                                                   | 52 |

|     | Investigation of different source-drain metal integration in a-IGZO TFT structures                   | 53 |

|     | Organic light emitting diode (OLED) with high stability                                              | 53 |

|     | Integrated organic thin film transistors for circuits application                                    | 54 |

|     | Vacuum deposited perovskite for p-type TFT                                                           |    |

| V.  | Life Sciences                                                                                        | 56 |

|     | Software development and signal processing for high throughput silicon multi-electrode array systems | 56 |

|     | Single cancer cell characterization using high-density microelectrode arrays                         | 56 |

|     | Electrical impedance assay for bacterial biofilm detection                                           | 57 |

|     | Mesoporous materials for biosensing applications                                                     | 57 |

|     | Photonic modulators                                                                                  | 58 |

|     | Single molecule sensing by nanopore field-effect transistors                                         | 59 |

|     | Characterizing bio-molecular interactions using fluorescence depolarization                          | 59 |

|     | Nanoengineering for antibacterial applications                                                       | 60 |

| VI. | Wearables                                                                                            | 61 |

|     | Capacitive measurement of non-ECG biopotentials                                                      | 61 |

|     | Validation of capacitive cardiorespiratory measurement in real world studies                         | 62 |

|     | Motion artifact reference sensor study for capacitive and contact biopotential measurements          | 62 |

|     | Reliable vital signs analysis with wearable sensors under ambulatory conditions                      | 63 |

|     | Channel-sharing design for high-density bio-signal recording applications                            | 64 |

|     | Psychophysiological stress detection in a semi-controlled environment                                | 64 |

|     | Analysis and fusion of wearable sensor data                                                          | 65 |

| VII | . Photovoltaics                                                                                      | 66 |

|     | Advanced thin film solar cell architectures                                                          | 66 |

|     | Novel carrier selective contacts for new concept silicon solar cells                                 | 66 |

|     | Measurement and demonstrators for innovative smart PV modules under non-uniform irradiation          | 67 |

|     | Modeling and measurement analysis of energy yield for advanced and smart PV modules                  |    |

|     | Defining optimal conditions for perovskite thin film PV solar cell performance measurements          |    |

|     | Wide-bandgap perovskite photovoltaics for high-efficient perovskite/silicon tandem solar cells       |    |

|     | Boosting the wind effects for increasing the energy production of photovoltaic modules                                  | 70 |

|-----|-------------------------------------------------------------------------------------------------------------------------|----|

|     | Next generation PV module technologies                                                                                  |    |

|     | Enhancing the energy production of photovoltaic module by advanced and novel concepts                                   |    |

|     | Silicon heterojunction (HJ) interdigitated back-contacted (IBC) solar                                                   |    |

|     | Integration of silicon heterojunction solar cells                                                                       |    |

| VII | II. GaN Power Electronics                                                                                               | 74 |

| IX  | . Sensor Solutions for IoT                                                                                              | 75 |

| Х.  | Wireless IoT Communication                                                                                              | 76 |

|     | High-speed DAC for future radar and mmwave sensing applications                                                         | 77 |

|     | Exploration of millimeter wave hybrid analog-digital architecture with realistic RF modeling                            | 77 |

| XI  | . Radar Sensing Systems                                                                                                 | 79 |

| XI  | I. Solid State Batteries                                                                                                | 80 |

|     | Conformal deposition of Li-ion conductors for 3D thin-film batteries                                                    | 80 |

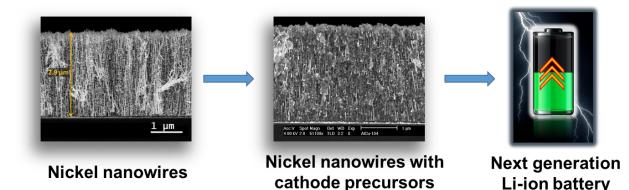

|     | Synthesis and characterization of cathode active materials for next-generation nano-engineered lithium-<br>batteries    |    |

|     | Solid-state thin-film batteries                                                                                         | 81 |

| XI  | II. Data Science and Data Security                                                                                      | 83 |

| XI  | V. Neuroelectronic Research (NERF)                                                                                      | 84 |

|     | Novel device for fluidic interfacing with the brain                                                                     | 84 |

|     | Unraveling neuronal activity during locomotion                                                                          | 85 |

|     | Engineering new devices and tools to study how the brain processes and stores information                               | 85 |

|     | Understanding memory through real-time processing and closed-loop manipulation of brain activity                        | 86 |

|     | Using machine learning and deep neural networks to automatically identify components of neural circui the visual system |    |

|     | Using virtual reality to study the function and neural circuits in the mouse visual system                              | 87 |

| XV. Microelectronics Design                                                                        |    |

|----------------------------------------------------------------------------------------------------|----|

| Structured ASIC development for space applications                                                 | 88 |

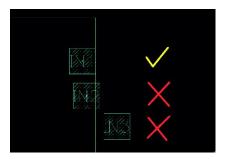

| Implementation of analog layout improvements                                                       | 88 |

| Development of RadHard LVDS IP in 65nm CMOS                                                        | 91 |

| Improvements to RadHard LVDS IP in 180nm CMOS                                                      | 92 |

| Single event transient test vehicle: characterization of a 65nm CMOS technology against heavy ions | 93 |

| Design of a clock phase extraction circuit for a high speed serial link                            | 94 |

| Design of RadHard Flip Flop with Razor technique                                                   | 95 |

| Automation and improvement of custom EDA flow                                                      | 97 |

## **Information**

Students from universities and engineering schools can apply for a Master thesis and/or internship project at imec. Imec offers topics in engineering (technology) and sciences in different fields of research.

All Master internship and thesis projects currently available at imec are collected in this topic guide. The projects are classified according to the imec expertises. You can find more detailed information on each expertise on <u>www.imec.be</u>. In addition, in this catalogue you will find the projects available with <u>imec.IC-link</u> and NERF (www.nerf.be)

## How to apply?

Send an application email including your motivation letter and detailed resume to the responsible scientist(s) mentioned at the bottom of the topic description you choose.

The researcher(s) will screen your application and let you know whether or not you are selected for a project at imec.

It is not recommended to apply for more than three topics.

There is no application deadline. We accept applications at any time and deal with them throughout the year.

Master internship students usually receive an allowance. However, some research groups only accept self-supporting students. Do you want to know upfront whether the project you wish to apply for provides financial support? When sending in your application email then check the remuneration details with the responsible scientist. For some projects, it is already mentioned in the project description that an allowance will not be provided.

For more information, go to the Master thesis & internship section on the Work at imec tab on www.imec.be. Do you have additional questions, then send an email to <u>student@imec.be</u>.

For Master thesis/internship projects in **imec the Netherlands** refer to http://www.holstcentre.com/careers/thesis-opportunities or contact <u>talent@imec-nl.nl</u>.

#### After acceptance

In case of acceptance to our internship program you are bound to embark on a very exciting and interesting experience! For imec, your contribution as a student will be essential in meeting the deliverables in our programs. Therefore, it is vital that - once you accept to come to imec - we can count on your commitment and dedication for the entire duration of the internship period.

## I. CMOS & beyond CMOS

## **3D** interconnect-based segmented bus architecture modelling and exploration

The communication and memory organisation in internet gateways and servers are a major source of energy consumption. Future technologies will lead to higher performances but also to an increased energy bottleneck. In this thesis, we want to build an exploration framework for comparing different 3D interconnect-based options for emerging processor and memory communication architectures. The main goal will be to reduce the overall energy consumption for given application workloads executed on this communication and memory architecture. Simulations will be performed based on available measurement data to calibrate the energy and performance models.

<u>Profile</u>: Strong interest in architecture exploration and simulation, basics of microelectronic technologies with emphasis on 3D interconnect schemes

<u>Type of project:</u> Internship project of 6 months (full-time, at imec Leuven) The start date of the project is Q2/Q3, 2017

Degree: Master in Engineering majoring in computer architecture or micro-electronics

Responsible scientist(s):

For further information or for application, please contact Eric Beyne (Eric.Beyne@imec.be) and Francky Catthoor (Francky.Catthoor@imec.be).

## Organic polymers for microbumps passivation

In order to increase the density of memory chips and improve the performance of logic devices beside scaling electronics devices, 3D integration is also necessary. Microbumps are interconnects between two stacked chips to make connection between them. Increasing density of interconnects or reducing pitch of microbumps in 3D integration to improve the performance of final product, requires new UBM (under bump metallurgies) materials and solder, cleaning and passivation options. The student will study cleaning and passivation of different UBM materials specially BZT organic polymers and their influence on IMC formation (intermetalic compounds) through papers and experimental results. Characterization techniques such as XPS, AFM, Contact angle, ... will be used in this study. 3D stacked chips will be analyzed using cross section, SEM and EDS analysis. Results will be presented in imec PTW weeks and then external conferences or journals.

### Type of project: Thesis project

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Jaber Derakhshandeh (Jaber.derakhshandeh@imec.be).

## Sub-nano engineered magnetic tunnel junction stacks for STT-MRAM applications

Future memory technology nodes will require faster, smaller, and more power-efficient devices. Since the conventional memories such as dynamic random access memory (DRAM) and static random access memory (SRAM) are reaching their scaling limits, new emerging memories are being developed. The perpendicular spin- transfer torque magnetic random access memory (STT-MRAM) is considered as a promising replacement. A high performance STT-MRAM stack contains up to 20 different layers, each of them around 1 nm or below. The key component of this memory is the perpendicular magnetic tunnel junction (p-MTJ) consisting of a CoFeB/MgO/CoFeB trilayer in which the CoFeB layers have a (001) texture lattice matched with MgO in order to obtain a high tunnel magnetoresistance (TMR) ratio and interfacial perpendicular anisotropy (PMA). Next to that, a variety of materials is being employed or evaluated in STT-MRAM stacks, each of them for a specific functionality. Co, Pt, Pd, Ni are being used in Co/Pt, Co/Pd, or Co/Ni multilayers as perpendicular synthetic antiferromagnets (p-SAF) for the pinning of the magnetization of one of the CoFeB layers [1-3].

The commonly used method to fabricate the STT-MRAM stacks is physical vapor deposition (PVD) in a cluster setup where all layers can be deposited without air exposure. The impact of the impinging atoms on the substrate during PVD deposition needs to be studied and controlled [I]. In the case of ultrathin films in the I-nm range commonly used in STT-MRAM stacks, sub-monolayer damage is no longer negligible since its functionality relies on interface effects such as interface induced PMA. From that perspective, preventing interface damage during deposition of a large atom, such as Ta, on top of a lower density material, such as CoFeB, is highly challenging, and can potentially limit the use of the material, despite its many advantages. Controlling the interface roughness and thickness is also required to enable the compatibility of the STT-MRAM stack with the high thermal budgets up to 400 °C that are applied when the stack is integrated into a CMOS process flow.

The student will conduct an experimental study of the impact of the impinging atoms during PVD deposition on the magnetic properties of sub-nm thin ferromagnetic films that are used in perpendicular STT-MRAM stacks aiming to improve the magnetic tunnel junction performance. Furthermore, in-situ annealing and cryogenic cooling will be investigated to improve further their structural and magnetic properties such as perpendicular anisotropy and tunnel magnetoresistance. The films will be deposited on 300 mm Si wafers using an industry relevant PVD multi-target cluster tool. Magnetic and electrical characterization is done by vibrating sample magnetometry, Kerr magnetometry, and current-in-plane tunneling. X-ray reflectivity, X-ray diffraction, SEM, TEM, rutherford backscattering will be used for structural characterization.

#### References:

Swerts et al., Appl. Phys. Lett., 106, 262407 (2015). Tomczak et al., Appl. Phys. Lett., 108, 042402 (2016). Devolder et al., Appl. Phys. Lett., 108, 172409 (2016).

<u>Type of project</u>: Internship project with a minimum duration of 4 months or thesis project with a minimum duration of 6 months, but preferably 12 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Materials Engineering, Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Johan Swerts (Johan.Swerts@imec.be) and Sebastien Couet (Sebastien.Couet@imec.be).

## Study of the kinetics of chemical reactions in nanostructures

In semiconductor manufacturing, new generations of devices have entered the nano-world, with critical dimensions smaller than 100 nm. Many process steps are still performed using aqueous chemistries, e.g. wet etching of materials for patterning and wet cleaning of surfaces. New transistor geometries are vertical, with the generation of I-D and

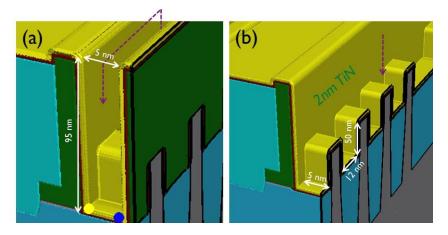

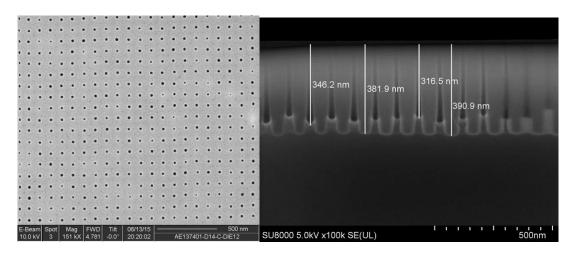

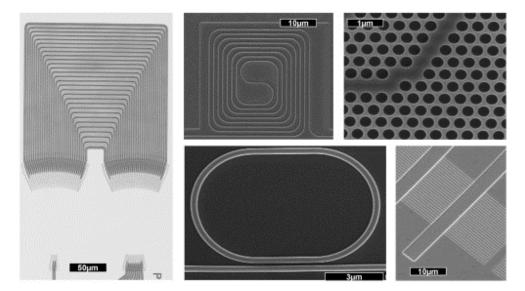

2-D nano-confined spaces (Fig. 1). Little is known about the kinetics of chemical reactions in nano-confined volumes. Chen et al. (2009) showed that the rate of enzymatic reactions was increased in nano-vesicles, while Okuyama et al. (2015) obtained a decreased etching rate for 1-D confined SiO2 nano-layers. Mechanisms affecting reaction kinetics at the nano-scale are not well understood. Chen et al. (2009) suggested that both an increased enzyme-substrate collision frequency and the enzyme-vesicle wall interactions may affect the reaction rate, while Okuyama et al. (2015) proposed that surface charges affected the concentration of reactive ions in the nano-slit.

In this project we investigate the kinetics of chemical reactions in nano-holes with 2-D confinement (Fig. 2). In a first part the etching behavior of metallic layers covering the wall of nano-holes with varying diameter will be studied (e.g. TiN using ammonia-hydrogen peroxide mixtures). The student will perform the wet etching tests, the data treatment of TEM (transmission electron microscopy) pictures generated by operators in the pilot-line, and a kinetic analysis. Results will be compared to etch rates obtained on planar films with film thickness measured by ellipsometry. In a second part the kinetics of reactions involving a SAM (self-assembled monolayer) deposited on the structures will be studied using ATR-FTIR (attenuated total reflection Fourier-transform IR spectroscopy). The method has already been developed and tested on nano-lines with I-D confinement, where a rate increase of 30% was observed. Here the student will prepare the ATR crystals (polishing), perform the FTIR tests using a home-build liquid cell, as well as the data treatment and interpretation. The content of the student project will be adapted depending on the progress of our research.

Figure 1. Cross-sections in a cartoon of a FINFET transistor after removal of the dummy gate (not to scale), showing (a) a nano-slit with 1-D confinement, (b) nano-holes with 2-D confinement.

Figure 2. SEM images of nanoholes: (left) top view, (right) cross-section view.

Type of project: Internship or thesis project or combination of both with a minimum duration of 3 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Nanoscience & Nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Guy Vereecke (Guy.vereecke@imec.be).

## Novel spin-on method to deposit self-assembled monolayers and thin polymeric films for surface and interface engineering in nano-IC applications

As the total transistors and interconnects sizes come down to few tens of nanometers and below, a shift in paradigm for the manufacture and integration of microelectronics components becomes apparent. Organic molecules - owing to their size, mechanical flexibility and chemical tunability - fit well in this slot and, thus, are expected to play a key role in IC downscaling. In this respect, self-assembled monolayers (SAMs) seem the best candidates. SAMs are a prototypical form of nanotechnology: the SAM precursor molecules carry the "instructions" required to generate an ordered, nanostructured material without external intervention. SAMs demonstrate that molecular-scale design, synthesis, and organization can generate macroscopic materials properties and functions. Although the details of the thermodynamics, kinetics, and mechanisms of assembly will differ significantly, these monomolecular films establish a model for developing general strategies to fabricate nanostructured materials from individual nanometer-scale components. Because SAMs can assemble onto surfaces of any geometry or size, they provide a general and highly flexible method to tailor the interfaces between nanometer-scale structures and their environment with molecular (i.e., subnanometer scale) precision. SAMs and polymeric films can control the wettability and electrostatic nature of the interfaces of individual nanostructures and thus their ability to organize into large assemblies and interact with overlayers adding chemical functionality, thermodynamic stability. While deposition on SAMs by dipping is already being extensively studied, thiol SAM spin-on from organic solvents is relatively unexplored. The first phase of this project will focus on the deposition and characterization (water contact angle, FTIR, XPS, AFM, ..) of thiol SAMs and eventually functionalized polymeric films on metal surfaces by spin-on from organic solvents. The study includes metal surface preparation before SAM deposition and the impact of post-SAM treatments such as anneal, gas flow and/or wet chemistries. The final aim of this work is to achieve a dense, ordered and defect-free SAM.In the second phase of the project we will focus on the scale-up of the SAM deposition process to 300mm wafers and on 300mm scale metrology techniques, such as light scattering, AFM, ellypsometry, mass measurement.

<u>Type of project</u>: Internship or thesis project or combination of both with a minimum duration of 6 months, but preferably 12 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Materials Engineering

#### Responsible scientist(s):

For further information or for application, please contact Silvia Armini (armini@imec.be).

## Machine learning based computational lithography

As the chip scaling continues technology node to node to follow Moore's law, computational jobs such as optical proximity correction (OPC) and design-for-manufacturability (DFM) have become too intensive to carry out with introduction of more design data and models (mask, optical, resist, etch, topography-aware and CMP) to improve chip printability and prediction accuracy. 'Big Data' usually refers to data volumes that are so large that traditional data processing applications are inadequate, which exactly represents current OPC and DFM confront. In consequence, increased risk with increased ramp-up time from research to high volume manufacturing has been

pointed out as risk as well as risks. The student will learn conventional OPC and DFM flow and work toward developing and applying "Machine learning" and optimization algorithms into OPC and DFM flow as a goal to I) reduce number of iteration, 2) reduce computational resource and 3) optimize/minimize DOE to shorten turn-around-time (TAT) in early develop and yield ramp up in Semiconductor manufacturing. Machine learning and optimization may include study of

- Pattern recognition (layout pixilation), Pattern extraction, Classification

- Machine learning Modeling training using optimization algorithm. Optimization incorporates mathematical and statistical concepts (effect, global/local min. search algorithm), or a new concept.

Type of project: Internship or thesis project or combination of both with a minimum duration of 6 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Computer Science, Electrotechnics/Electrical Engineering, Nanoscience & Nanotechnology, Physics

### Responsible scientist(s):

For further information or for application, please contact Ryan ryoung-han kim (Ryan.ryoung.han.kim@imec.be) and Jae Uk Lee (Jae.uk.lee@imec.be).

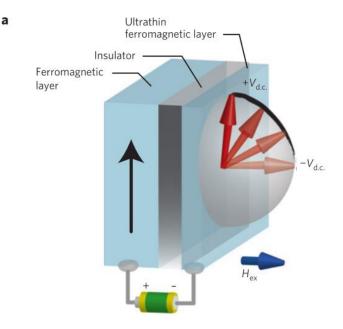

## The giant Voltage Control of Magnetic Anisotropy (VCMA) effect for enabling next generation spintronics and magnetic memories

The dynamic control of magnetic materials using an electric field enables key applications in the fields of magnetic memories (MRAM), and spin-based logic. In particular, the possibility to modulate the magnetic anisotropy of a ferromagnetic metal using VCMA [1] has the potential to decrease the energy consumption of magnetic technologies by several orders of magnitude. However, the currently achieved magnitude of the VCMA effect is not sufficient for a groundbreaking application.

In this project, the student will explore one of the two following aspects of VCMA, depending on the available experimental material and their inclination:

- the optimization of the VCMA effect, through engineering the materials and the interfaces involved in VCMA or;

- the applications of the VCMA effect in spin-based logic, through micromagnetics simulations and electrical characterization of devices.

- In both cases, the student will work with specialized materials, techniques and tools to meet the requirements of this advanced topic.

[1] Maruyama et al., Nature Nanotechnology, 4, 158 (2009)

[Figure] Nozaki et al., Nature Physics, 8, 492 (2012)

Type of work: The work will consist of 10 % literature study and 90 % experimental and modeling work.

## Type of project: Thesis project

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

## Responsible scientist(s):

For further information or for application, please contact Bart Vermeulen (Bart.vermeulen@imec.be) and Koen Martens (Koen.martens@imec.be).

## In-situ electron beam study of fracture events to assess the strength and compliance of advanced BEOL structures at the nanoscale

Chip-package interaction is a critical reliability issue for Si microelectronics chips with Cu/low-k Back-End-Of-Line (BEOL) interconnects. Package processing causes high vertical and shear forces to the thin BEOL layers, which might result in fracture or delamination. As the technology advances, the interconnect structures continue to evolve with decreasing dimensions, increasing porosity of intermetal dielectrics and an increasing number of layers and complexity. The introduction of advanced materials on both chip and package level and the harsh environmental conditions during processing and operational use cause additional challenges for reliability analysis and prediction. In the microelectronics industry, current materials selection is made with limited understanding of elastic properties, fracture properties and interfacial adhesion of thin continuous films deposited on a silicon substrate. However, these parameters do not sufficiently represent the failure behavior and structure stability of multilevel interconnects, where each material exist as an individual part with different shapes and various cross-section geometries. To gain more insight into root causes of failure processes, the semiconductor industry needs reliable, reproducible testing methods and strategies to monitor these parameters, not only for low-k dielectric films, but also for complete interconnect stacks. Therefore, a careful characterization of the mechanical stability of potential new low-k candidates is required to integrate these new materials and Cu interconnects and assure reliability during chip packaging and under field conditions. To capture the fracture onset and crack propagation, high-resolution real time techniques are preferred over post mortem observations. Electron beam based methods are one of the most commonly used techniques for in-situ studies, since they yield a high lateral resolution without additional specimen preparation. The focus of this work lies on the development and application of new in-situ nanoindentation and electron beam based mechanical test methodology to assess the strength and compliance of BEOL structures at the nanoscale and to provide quantitative data that can be used to determine allowable chip/package interactions. The master student will work on: definition of test structures (ex. films, beams or pillars), sample preparation and mounting in a SEM or nanoindenter, application of mechanical forces inside the SEM or nanoindenter on the test structures and monitoring in-situ the effects (force-displacement and crack formation), scientific analysis of the results.

### Type of project: Thesis project

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Materials Engineering, Mechanical Engineering, Nanoscience & Nanotechnology, Physics

### Responsible scientist(s):

For further information or for application, please contact Kris Vanstreels (Kris.vanstreels@imec.be), Ingrid De Wolf (Ingrid.dewolf@imec.be) and Jin Won (Maria) Seo (Maria.seo@kuleuven.be).

## Full-zone band structure calibration for the quantum mechanical simulation of confined III-V TFETs

As scaling of semiconductor components enters the nanometer regime, the increase in power density becomes an important bottleneck. The root cause lies with the 60 mV/dec limit on the subthreshold swing of a classical MOSFET, which causes large leakage currents if the supply voltage is scaled too aggressively. Alternative transistor concepts, based on quantum mechanical tunneling, are able to circumvent the subthreshold swing limit thanks to their different current injection mechanism. Among the most promising concepts in this category is the tunnel-FET (TFET). The TFET relies on band-to-band tunneling, which allows for sub-60mV/dec subthreshold swing and low leakage currents. To obtain sufficient ON-currents, TFET research is focusing on III-V materials, which exhibit a wide range of effective masses and bandgaps.

To model this new type of transistor and the new material systems, accurate quantum mechanical simulation tools are required. At imec, we have therefore developed Pharos, a quantum simulator for III-V TFETs. Pharos relies on a band structure calculated with the k.p method. It is the first such simulator that captures the full first Brillouin zone. This full-zone capability is especially important when investigating very confined structures, such as nanowires. However, there is a lack of reliable full-zone k.p parameters in literature, which limits the applicability of the simulator in confined structures.

The goal of this thesis project is therefore to obtain a calibration procedure for k.p band structures of III-V materials and to use the calibrated parameters to simulate confined TFET structures. After gaining proficiency in the k.p band structure method, the student will carry out a full-zone calibration of k.p band structures to an abinitio reference for several relevant III-V materials. The student can start from an existing rudimentary algorithm. The goal is to obtain a calibration procedure that is transferable to other materials as well. Once calibrated parameters have been obtained, the student will use imec's in-house developed quantum simulator Pharos to investigate strongly confined TFET structures. He/she can then assess the utility of the calibrated band structures in the design of next generation TFETs.

For this challenging topic a good knowledge of semiconductor physics and semiconductor devices is required, as well as a solid background in quantum mechanics. The research will be carried out in the TFET team at imec, which has extensive experience in characterization and quantum mechanical modeling of tunneling-based devices.

#### Type of project: Thesis project

Degree: Master in Science and Master in Engineering majoring in Nanoscience & Nanotechnology, Physics

## Surface chemistry and atomic layer etching of III-V semiconductors for 5 nanometer CMOS technologies and beyond

The ultimate scaling limit of Si-based complementary metal-oxide semiconductor (CMOS) technology is rapidly approaching. Despite the excellent properties of the group IV semiconductor and its native oxide, the continued reduction of the dielectric oxide thickness has necessitated the use of high-k gate dielectrics and a metal gate. At present, the performance enhancement for Si-based transistors can no longer be guaranteed due to intrinsic mobility issues. The considerably higher mobility of III-V compound semiconductors (i.e. InGaAs, InAs, InSb) has led to renewed interest and a following phase in the development of extremely scaled transistors for 5 nm technology nodes and beyond. Wet-chemical treatment (e.g. for layer selective etching, surface and interface passivation, removal of native oxides, channel trimming, etc.) are an essential part of device fabrication. Due to the very small transistor dimensions etching selectivity and control at the (sub)atomic-layer-scale is required. In order to design wet-chemical etchants that can be used for this purpose, insight in the interactions between surface atoms and molecules in chemical solutions is required. For atomic layer etching, a kinetically controlled dissolution reaction is preferred, because hydrodynamic conditions are generally more difficult to control. Semiconductor dissolution processes are known for their complexity. Charge transfer reactions between valence and conduction band electrons and oxidizing species, chemical interactions, surface states, bond rupture, oxide formation and dissolution all need to be considered in order to obtain fundamental insight in the surface chemical and electrochemical etching process. Apart from (photo)electrochemical etching, two forms of "open-circuit" etching can be distinguished which generally require an oxidizing agent. In chemical etching, valence electrons are transferred directly from surface bonds to the oxidizing agent, giving rise to rupture of the bonds and dissolution of the solid. In electroless etching, the oxidizing agent removes electrons from the valence band of the solid; this is equivalent to injection of holes. The holes are mobile and, if localized in surface bonds, cause bond rupture and dissolution. Such chemical and electroless dissolution mechanisms can have a significant impact on surface properties after chemical treatment. In the former case they can be exploited for surface morphology control while in the latter case non-stoichiometric dissolution can result in build-up of elemental species which may induce undesired electronically active bandgap states detrimental to interface formation. During this internship the main focus will be on the group III arsenides. At present, the surface (electro)chemistry of these semiconductors during atomic layer etching is not well understood. Of special interest is the role of anions on the surface chemical and electrochemical reactions. Careful mapping of parameter space (In/Ga content, acid concentration, redox species, temperature, etc.) will provide insight. A large variety of analytical techniques are available at imec. Inductively coupled plasma mass spectrometry and various electrochemical methods are used to obtain insight in oxidation/dissolution kinetics and stoichiometry. Further mechanistic insight is be obtained by studying the surface chemistry with x-ray photoelectron spectroscopy, photoluminescence, elastic recoil detection, (conductive) atomic force microscopy, profilometry, scanning and transmission electron microscopy.

<u>Type of project</u>: Thesis or internship project with a minimum duration of 4 months

Degree: Master in Science majoring in Chemistry/Chemical Engineering, Nanoscience & Nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Dennis van Dorp (vandorpd@imec.be).

## Edge placement error budgeting in CMOS process flow

With the continuous shrink of technology nodes, lithography becomes more and more challenging. At 20 nm node, double patterning technology (DPT) was the usual way of achieving the fine device structures. Until EUV is available as a high volume manufacturing (HVM) solution, DPT or triple patterning technology (TPT) will be required to sustain scaling. However, as the industry goes forward with scaling, for sub-14 nm nodes the chip manufacturers are anticipating three or four masks per layer. Exposing the patterns separately allows the spacing or pitch of the structures to be reduced by a factor of two (or more for triple/quadruple patterning) while increasing the metrology and inspection challenges. As multiple masks are used for patterning one layer, placement of individual layers as well as pattern variations within each layer becomes important for these extremely small structures. To assess these small changes CD-SEM's are used. Starting from standard CD (Critical Dimension) measurement approaches, the industry quantifies the printability performance on wafer based on SEM (Scanning Electron Microscope) pictures and algorithms that determine distances (CD) at specific locations. Once these measurements are acquired, the performance of the lithographic process needs to be evaluated. Position of each pattern is of utmost importance as we scale from node to node. In such a scenario pattern placement error determination is one of the key requirements for assessing the yield of device structures. Determination of this PPE/EPE(edge/pattern placement error) budget for particular process flows needs to be done so that the right process assumptions can be made for particular node.

The purpose of this internship is to come up with an analysis method where we should be able to do EPE budget analysis for the 7nm node and below. Data collected on specific features of interest (contours) need to be evaluated in different ways. At the end of the project we should be able to come up with a tool in Matlab which will help in determination of PPE budgets as well as plot them.

Required skills: MatLab GUI development, programming skills

Type of project: Internship project with a minimum duration of 6 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Sandip Halder (halder@imec.be), Philippe Leray (leray@imec.be) and Anne-Laure Charley (charley@imec.be).

## Automatic recipe and data management development for Fab automation

#### Background:

For operational excellence of semiconductor fabrication process at pilot line, recipe management is important in order to avoid any human error, such as wrong recipe selection by operator and wrong recipe file naming by engineer. Therefore, a recipe management system needs to be developed to check recipe name and to filter wrong recipe. Not only recipe management, but also data management in metrology tool is critical in order to deliver data to end user. To do so, data management SW needs to be developed.

<u>Task</u>:

- 1. Development of software and (or) script for recipe list generation and checking recipe name by a recipe name convention rule and filtering recipe against the rule.

- 2. SW/Script development for data export to a data storage location.

#### <u>Goal</u>:

Software and script development for recipe management on ellipsometry and for result data management on automatic automic force microscopy.

<u>Type of project:</u> Internship project

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Computer Science, Electrotechnics/Electrical Engineering, Materials Engineering, Mechanical Engineering, Nanoscience & Nanotechnology, Physics

Responsible scientist(s):

For further information or for application, please contact Tae-Gon Kim (tae-gon.kim@imec.be).

## Computational methods to assess the mechanical properties of thin films

Owing to the achievements in the continuous scaling of integrated circuits and the maximization of the transistor density, performance and functionality of the microelectronic devices have been improving rapidly for many years. Introduction of new materials, chip designs, processes and packaging strategies that can cope up with the everdecreasing dimensions have been one of the key factors to provide the sustainability of these advancements. However, the integration of these new materials to the architectures that are shrinking in dimensions and increasing in complexity, has proven to be a difficult task so far, due to a number reliability issues. A significant portion of these issues are linked to the inferior mechanical reliability. Therefore, it is important to explore and assess the mechanical properties of the constituents and evaluate their suitability for the future technology nodes. Nanoindentation is the most commonly used technique for this purpose due to its accuracy, wide range of capabilities to assess different aspects of material behavior and straightforward data analysis procedure on bulk materials. In the case of thin films however, the properties of the underlying substrate may influence the response and obscure the accurate interpretation of the experimental data. This phenomenon is known as the "substrate effect". The magnitude of this effect is influenced by and interrelated with many parameters such as the nanoindenter geometry, indentation depth, the material properties of both the film and the substrate, the film thickness, among others. Imec has a potential solution to obtain substrate independent mechanical properties. The solution is based on a number of computational methods and formulas applied successively to the experimental data obtained through nanoindentation measurements. The solution is currently verified for a limited range of conditions. However, it is desired to extend the application to a wider range of material groups and measurement conditions. In order to achieve this goal, a software with a graphical user interface which allows to perform rapid calculations and easy manipulation of the computational parameters are required. The goal of this study will be to create the algorithm, software and the graphical user interface to implement this methodology. The student will then apply and test the technique for a variety of measurement conditions and search for possible improvements. The details of the computational approach as well as the necessary experimental data and software tools will be provided to the student. Guidance on the nanoindentation technique and interpretion of the experimental data will also be provided. The student must have profound interest in computer programming and has experience and/or knowledge. A physics and/or material science background is an additional advantage.

### Type of project: Internship project

<u>Degree:</u> Master Science and Master in Engineering majoring in Materials Engineering, Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Kris Vanstreels (kris.vanstreels@imec.be), Ingrid De Wolf (ingrid.dewolf@imec.be) and Oguzhan Orkut Okudur (oguzhan.orkut.okudur@imec.be).

## Atomic layer deposition of metal doped HfO2 as ferroelectric material for future memory technologies

Several metal doped HfO2 deposited by atomic layer deposition have shown ferroelectric behavior making the system a potential choice for IT and IT-IC ferroelectric memory solutions [1]. In 2011 it was observed that deviations from the commonly assumed polymorphism of HfO2 or ZrO2 (monoclinic - tetragonal-cubic) is possible with the formation of an intermediate non-centrosymmetric orthorhombic phase having ferroelectric behavior [2]. The concentration of dopant metal (e.g. Al, Si, Gd, Sr) in the HfO2 host can be controlled at the atomic level by dopant: Hf pulse ratio during the self -limiting growth characteristic to the atomic layer deposition process [1]. By using sequential exposures, gas phase reactions between the precursors are avoided and the thin film grows solely by surface reactions. The post-deposition anneal after the deposition of mechanically constraining capping layer(s) triggers formation of orthorhombic phase [1]. The project involves literature study as well as the experimental investigation of doped HfO2 deposition and their physical properties. Post-anneal of the samples will be an important step in creation of the orthorhombic phase. Evaluation of strain induced by the capping layer by ellipsometry will give further understanding how to control the orthorhombic phase formation. The samples will be characterized by techniques such as X-ray reflectivity (XRR), grazing incidence X-ray diffraction (XRD), and grazing angle attenuated total reflectance Fourier transform infrared GATR-FTIR. Dielectric constant and ferroelectric behavior will be evaluated from capacitance-voltage and polarization -voltage measurements. Further analyses, e.g. Rutherford backscattering spectroscopy and atomic force microscopy (AFM) will be performed in collaboration with imec's material characterization group.

1. Michael Hoffmann, Tony Schenk, Ivan Kulemanov, Christoph Adelmann, Mihaela Popovici, Uwe Schröder & Thomas Mikolajick, Low Temperature Compatible Hafnium Oxide Based Ferroelectrics, Ferroelectrics, 480:1, 16-23 (2015).

2. T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, Ferroelectricity in hafnium oxide thin films, Appl. Phys. Lett., 99(10), 102903 (2011).

Type of project: Internship or thesis project with a minimum duration of 6 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

Responsible scientist(s):

For further information or for application, please contact Mihaela Popovici (popovici@imec.be).

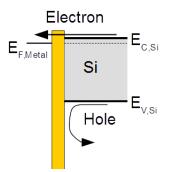

## Advanced Source-Drain contact resistance

Throughout the previous decades ever faster, smaller and cheaper computers have revolutionized our life. The main driving force behind this has been the shrinking of the basic building block of digital circuits, the metal-oxide-semiconductor (MOS) transistor. The MOS transistor is a digital switch with a low resistance ON state and a high resistance OFF state, so the channel resistance thus must be kept to a minimum level. Therefore the source and drain contact resistance becomes more and more important in the total source-drain resistance.

The main factors that determine the contact resistance are next to contact area, the actual Schottky Barrier Height and the dopant activation near the interface. The Schottky Barrier Height is not simply related to the contacting metal work function but suffers from fermi level pinning (FLP). This FLP can be reduced by the introduction of an interfacial layer or other interface treatments, to remove the FLP with minimal resistance introduced.

This module team selects and tests materials and processes on different semiconducting source-drain materials, Si, Ge, SiGe and InGaAs, for n and p MOSFETs, to reduce the contact resistance. Materials and processes are not

restricted to those available at imec, but often samples are sent to other companies for special processes. E.g. hot or cryogenic implantations and laser treatment are used to increase the concentration of activated dopants. Special film deposition and thermal treatments are used to reduce the contact resistivity further. A simple test structure is the work horse to allow fast screening; the processing and electrical analysis were optimized to maximize the performance. Often, after initial electrical analysis a wafer is cut into serval coupons which can each be given a thermal treatment and are measured again afterwards.

The emphasis of this work is on electrical measurement of these contact structures and on analysis of the electrical data, together with the team, to link the electrical data to the experimental variations and build understanding of the relation between physical and electrical properties. Another output of this work is to select materials with optimal properties from these screening experiments, for application at contacts in advanced devices.

### Type of project: Thesis project with a minimum duration of 6 months

<u>Degree:</u> Master in Engineering Technology and Master in Engineering majoring in Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Marc Schaekers (Marc.schaekers@imec.be).

## 3D chemical analysis of microelectronics systems

One driver of the semiconductor industry growth is the sustained realization of "Moore's Law", whereby the number of transistors in an integrated circuit doubles approximately every 2 years with an associated increase in circuit functionality, reduction in operational power, and, most important, a reduction in unit cost. These fast technological developments, including increased process and material complexity, as well as reduced tolerance levels for process excursions have increased the need for a more controlled manufacturing environment necessitating equivalent improvements and developments in metrology. The present evolution towards merging lab and Fab metrology implies that these developments are necessary for use both in the R&D phase as in the final production phase. 9 With the strong size dependence of many material problems and phenomena, metrology needs to be performed more and more on devices with realistic dimensions and on wafer scale. Imec has recently acquired a new metrology tool combining a TOF-SIMS (Time of Flight Secondary lons Mass spectrometry) and an AFM (Atomic Force Microscope) instrument. This instrument is designed in order to combine chemical information from the TOF-SIMS with topographical information from the AFM, allowing 3D chemical mapping of samples. The objective of this thesis is to establish this AFM/TOFSIMS system as a 3D-metrology tool. For this objective, the AFM module will be used purely in topographic mode. The first part of the thesis will be devoted to the qualification of this new instrument to establish its ultimate performances, before applying it to model system. These systems will be chosen from technologies from the BackEnd-OF-Line (dual damascene). In these systems, etching of trenches occurs via a Reactive Ion Etching step, leaving polymer residues on the structures. These residues need first to be cleaned before metal deposition can occur and a detailed chemical analysis is frequently needed to determine the optimum cleaning process and its efficiency. This can be evaluated by XPS on specifically designed structures . However, the information content of TOFSIMS for organic contaminants is much higher than from photoemission, hence TOFSIMS is a preferred analysis approach. Unfortunately, the topography on the line arrays prevents a full 3D reconstruction of TOFSIMS profiles. The application of the 3D-TOFSIMS system using the in-situ AFM represents an important step forward in this case. After filling the trenches with Cu, one still has no or limited physico-chemical information on the 3D Cu concentration in the ILD between Cu lines. A prominent challenge one faces in analyzing these structures, is that when using sputtering for depth profiling, topography is developing during the analysis due to large difference in erosion rate between the different materials. This thesis will show that this problem can be solved using TOFSIMS-AFM by monitoring the topography growth and implementing correction procedures. The output will be protocols for quantitative composition profiles for heterogeneous and non-planar systems.

Type of project: Thesis with internship project with a minimum duration of 6 months

<u>Degree:</u> Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Materials Engineering, Physics

Responsible scientist(s):

For further information or for application, please contact Alexis Franquet (Alexis.Franquet@imec.be), Thierry Conard (Thierry.Conard@imec.be) and Valentina Spampinato (Valentina.Spampinato@imec.be).

## Atom Probe Tomography for future 3D metrology applications

The enhancement in semiconductor device performance has for many years been readily achieved through device scaling i.e. the fabrication of smaller devices. However, this approach is becoming more challenging and to meet the semiconductor roadmap, alternatives to complement scaling are being explored. These involve the use of semiconducting materials other than conventional Si and include SiGe, Ge, GaAs, InGaAs, GaN, InP, etc. Moreover, there is also a significant move away from planar i.e. 2D, device architecture towards 3D device structures. These changes mean that the metrology used for quantifying such structures also needs to adapt. Laser assisted Atom Probe Tomography (APT) is one technique which could provide the 3D quantitative analysis required with an excellent sensitivity (10 ppm) and near-atomic spatial resolution (~0.2-0.3 nm). In simple terms, APT exploits the concept of field evaporation and ionization of atoms from the apex of a needle-shaped specimen (~50 nm tip radius) and their projection onto a position sensitive detector. By taking the reverse projection of the detected ions, a tomographic reconstruction of the specimen is obtained and a full 3D quantitative analysis achieved. However, as the technique is still in its infancy for semiconductor materials, there are numerous challenges still to be overcome. This will only be achieved through a better knowledge into the underlying physics of the technique e.g. laser-sample interaction, tip heating and atom migration etc. The objective of this internship/master's thesis is therefore twofold; to join a research team currently working on addressing the underlying physics facing APT by analyzing the semiconductor materials (and their combinations) of tomorrow (e.g. compounds, oxides, heterogeneous materials) with the objective of establishing a fundamental understanding of the measurement artefacts, their root causes and determining a means to correct for them. Secondly, it offers an excellent opportunity to gain experience and an insight into state of the art scientific instrumentation (e.g. focused ion beam secondary electron microscopes and two APT instruments) and the semiconductor materials being developed for future technology. Due to the ongoing activities of the team, a more detailed project of research (or options depending on the situation) will be outlined closer to the time.

Type of project: Internship or thesis project or combination of both with a minimum duration of 6 months

Degree: Master in Science and Master in Engineering majoring in Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Richard Morris (richard.morris@imec.be), Claudia Fleischmann (claudia.fleischmann@imec.be) and Janusz Bogdanowicz (Janusz.bogdanowicz@imec.be).

## Seeding and growth of boron-doped diamond thin films

Diamond is outforming other materials in many domains such as hardness, wear resistance, thermal conductivity, chemical inertness, and biocompatibility. As it can be made electrically conductive (p-type) by boron doping, borondoped diamond thin films look especially attractive for electrical applications. They are being explored and developed for a wide range of applications including chemical treatment (e.g. waste water, swimming pool, chemical solutions), nanoscale electrical probes, implantable bio-electrodes, and water splitting/hydrogen generation.

The goal of this internship is to obtain better insight into the interfacial growth of boron-doped diamond layers. For this, the student will seed and grow diamond layers using imec's hot-filament chemical vapor deposition (HFCVD) reactor using different doping levels, seeding densities and growth parameters. The electrical analysis at the nanoscale is carried out on the interfacial side using electrical AFM methods such as SSRM and conductive AFM (c-AFM) for studying the grain and grain-boundary conductivity. Here, we look for a correlation between boron doping level and grain conductivity. Furthermore, a comparison of doped versus undoped diamond seed nano-crystals is done. The conversion of a seed layer into a highly conductive interfacial layer is not completely understood yet and is therefore

investigated in detail in this study. For physical analysis, scanning electron microscopy (SEM), RAMAN, and elastic recoil detection (ERD) are used.

For this topic, the student will work inside a lab and cleanroom environment to carry out the required experimental steps. The student will characterize the fabricated samples by different characterization techniques. The student will be part of imec's materials and component and analysis group.

<u>Type of project</u>: Internship or thesis project or combination of both with a minimum duration of 6 months

<u>Degree:</u> Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

Responsible scientist(s):

For further information or for application, please contact Thomas Hantschel (Thomas.Hantschel@imec.be).

## Electrical SPM for the analysis of magnetic memory

Spin-transfer torque magnetic resistive memory (STT-MRAM), is emerging as a potential replacement for Flash and/or DRAM applications, as they exhibit non-volatility, high-speed, low-voltage switching and almost unlimited read/write endurance. However, significant challenges toward the widespread commercialization of this technology are still in the area of process scaling, materials integration and physical operative mechanisms. In this context, electrical scanning probe microscopy (SPM) techniques such as (C-AFM, KPFM and SSRM) represent invaluable tools for the analysis of post-patterning treatment and material selection in magnetic tunnel junctions, as they allow the probing of nanoscaled features. This internship/thesis fits into the characterization framework for STT-MRAM using a set of electrical SPM techniques. You will be trained in the use of the tool and you will intensively use it focusing on device characterization and AFM-analysis. The data analysis and interpretation will cover an important part of the work; you will apply statistical principles in data collection and will be asked to rule out your results. You will work in an international R&D team; a good command of English language is required. The detailed content of the work will be defined in detail at the moment of starting this project.

Type of project: Internship or thesis project or combination of both with a minimum duration of 6 months

<u>Degree:</u> Master in Engineering Technology, Master in Science and Master in Engineering majoring in Chemistry/Chemical Engineering, Electrotechnics/Electrical Engineering, Materials Engineering, Nanoscience & Nanotechnology, Physics

#### Responsible scientist(s):

For further information or for application, please contact Umberto Celano (Umberto.Celano@imec.be).

## Advanced analysis of Rutherford backscattering spectrometry through parallel processing

This work will be executed at imec, which is the leading European micro-electronics research center. Imec does research on a wide variety of front edge micro-electronic devices and applications (transistors, memories, solar cells,...). To verify the correct fabrication of these extremely challenging new devices (sub-22 nm technology) also high end characterization tools are essential. In this framework accelerator based characterization is one of the approaches that is pursued. For this, imec operates a 2 million Volt tandem particle accelerator, connected to multiple beam-lines and detection end-stations (vacuum chambers) maintained at high vacuum. The experimental results (spectra) are compared to physical models to quantify the properties of the fabricated devices.

As of now, the optimization of the model towards the experimental result is achieved by least squares fitting (fitting) using the grid-search or Levenberg-Marquardt algorithm. In this scheme, due to the computational demand, only a few parameters can be fitted (at once), and the analyst needs to supervise and steer the analysis constantly -a lengthy and labor intensive activity.

The purpose is develop a new software program for the analysis of the experimental results. We will implement new algorithms for the optimization that lend themselves better towards parallelization, for example the differential evolution algorithm. Besides, the student will also prepare the necessary code to allow for parallel operation on multiple cores and demonstrate its advantages.

The main tasks will be:

- To implement alternative optimization algorithms, for example the differential evolution algorithm.

- To investigate the performance of the new optimization method.

- To prepare the new program to allow its execution on multiple cores.

This subject is an opportunity for those who wish to get in-depth experience in "Big data" analysis strategies. Meanwhile, the student will gain practical experience with multi-core and parallel processing and on computational optimization.

<u>Type of project</u>: Thesis project or thesis combined with internship project with a minimum duration of 6 months

Degree: Master in Science and Master in Engineering majoring in Computer Science, Physics

### Responsible scientist(s):

For further information or for application, please contact Johan Meersschaut (Johan.Meersschaut@imec.be).

## Embedded distributed human-machine application for accelerator based metrology

This work will be executed at imec which is the leading European micro-electronics research center. Imec does research on a wide variety of front edge micro-electronic devices and applications (transistors, memories, solar cells,...). To verify the correct fabrication of these extremely challenging new devices (sub-22 nm technology) also high-end characterization tools are essential. In this framework accelerator based characterization is one of the approaches that is pursued. For this, imec operates a 2 million Volt tandem particle accelerator, connected to multiple beam-lines and detection end-stations (vacuum chambers) maintained at high vacuum. Continuous and ongoing improvements and investments to the detection systems and the control software allow us to be internationally at the forefront regarding ion-beam based metrology for microelectronics applications.

This subject involves the implementation of a distributed embedded control application (WASP) to enable the accelerator based metrology at imec. This project aims at the development of a new software package for the control of the system in a modular and naturally multi-threaded concept. In particular, the software allows to communicate with single devices through Ethernet (TCP/IP) and RS232/RS485 (via Serial-Ethernet gateways) and with the user through a user-friendly graphical interface (GUI) as well as support for a flexible scripting language capability.

The new software architecture is designed such that new devices can be connected and disconnected dynamically during the operation, and the devices appear as virtual instruments on the screen. The signals from various virtual instruments are accessible to both the GUI as well as to scripts that can be run in a command-like environment.

The WASP concept was originally designed to control the hardware and data acquisition. However, the concept potentially may also be very powerful and useful to realize an on-line data analysis. The algorithms to perform the data analysis are available, but at this moment the analysis has to be manually initiated and supervised by the analyst. The main tasks will be:

- To implement communication drivers, so-called daemons or services, (with stepper motors, data acquisition, counters, data analysis routines) in the Visual C++ environment using WinForms.

- To implement a graphical user interface in HTML + Javascript to run with Windows' Hypertext Application environment (HTA)

- To implement the same functionalities in Javascript to run in the console with node.js

This subject is an opportunity for those who wish to experience the aspects of programming in C/C++, Javascript, HTA, and node is based environment for the development of human-machine interfacing and automation.

<u>Type of project</u>: Thesis project or thesis combined with internship project with a minimum duration of 6 months

Degree: Master in Engineering Technology majoring in Computer Science

Responsible scientist(s):

For further information or for application, please contact Johan Meersschaut (Johan.Meersschaut@imec.be).

## One-dimensional carrier profiling of blanket and confined semiconducting structures

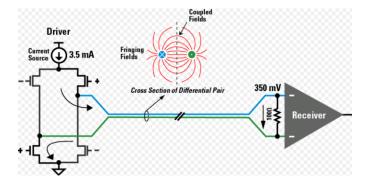

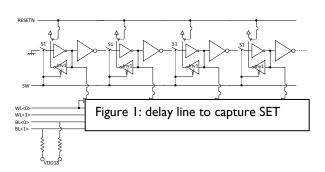

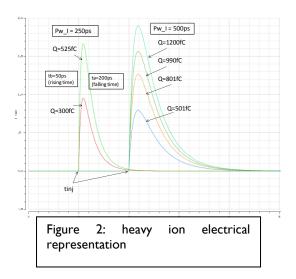

The performance increase of Complementary Metal Oxide Semiconductor (CMOS) devices at every new technology node has required to shrink their dimensions to the nanoscale and to introduce new high-mobility channel materials (Ge, SiGe, III-V). More recently, these devices have also moved from planar to three-dimensional architectures. In this context, it is urgent to develop a characterization technique able to accurately determine the incorporation and activation of dopants in the ultra-shallow doped regions of the transistors, i.e. the source, drain and extensions. This project aims at tackling this critical issue by combining two established techniques, i.e. Secondary Ion Mass Spectrometry (SIMS) and microhall (MH). SIMS is the established technique for one-dimensional dopant profiling. In a nutshell, SIMS is based on the layer-by-layer sputtering of the sample with the help of a low-energy ion beam. The fraction of the sputtered atoms which are ionized is accelerated by an electric field to a mass spectrometer, where each species is separated and counted. Unfortunately, SIMS does not capture any electrical information about the sample as it measures the total dopant profile, i.e. including the inactive portion. In this project, we propose to incorporate multiple MH measurements during the sample sputtering to determine the active doping concentration at different stages of the profiling. This project will essentially consist of two tasks. Task I will deal with simple blanket structures of doped Si and more advanced SiGe, Ge and III-V materials. MH measurements will be run either on the sputtered surfaces or on dedicated metallic pads to improve the electrical contacts. Task II will extend the technique to confined three-dimensional volumes. For this purpose, dedicated structures have been fabricated, where fin arrays of dimensions compatible with SIMS have been electrically connected in parallel such that their electrical resistance can be measured. In both tasks, the candidate will focus on the MH measurements and simulations. Calculations will indeed also be needed to understand the impact of the contact geometry and of the confinement on the free carriers and currents inside the investigated structures.