# Master Thesis & Internship Projects @ imec

| nformation |  |

|------------|--|

|            |  |

| I. | CMOS & beyond CMOS                                                                                                                               | 7  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | Machine learning based computational lithography                                                                                                 | 7  |

|    | Ferroelectric device electrical characterization                                                                                                 | 7  |

|    | Selective low-k dielectric growth using metal nitride conversion approach                                                                        | 8  |

|    | Impact of thermal budget on spin-orbit torque and SOT-MRAM performances                                                                          | 9  |

|    | Low temperature epitaxial growth of Ga doped SiGe for future device applications                                                                 | 10 |

|    | Study of an optical metrology technique for advanced semiconductor process control                                                               | 10 |

|    | Spin wave-like excitations in low-dimensional ferromagnets                                                                                       | 11 |

|    | Time-dependent Ginzburg-Landau simulations for superconducting rings                                                                             | 12 |

|    | Modeling of Transmon Qubits                                                                                                                      | 13 |

|    | Cross-layer memory organisation simulation and exploration framework                                                                             | 14 |

|    | Chemical mechanical polishing of new materials                                                                                                   | 14 |

|    | Photoresist line edge roughness and smoothing techniques in EUV lithography                                                                      | 15 |

|    | Light-matter interaction in organic and inorganic photoresists for EUV lithography                                                               | 16 |

|    | Simulations for semiconductor quantum dots                                                                                                       | 17 |

|    | Novel spin-on method to deposit self-assembled monolayers and thin polymeric films for surface and interface engineering in nano-IC applications | 18 |

|    | Fundamental study of SiCO, poly Si and SiO2 in Quasi-atomic layer etch mode                                                                      | 18 |

|    | Modeling of magnetoelectric coupling for advanced spintronic applications                                                                        | 19 |

|    | Spintronic devices based on spin waves for beyond CMOS applications                                                                              | 20 |

|    | Reliability assessment of RRAM memory devices                                                                                                    | 20 |

|    | Magnetism in graphene for spin-orbit torque (SOT) devices                                                                                        | 21 |

|    | Thermal degradation mechanisms in III/V – dielectric stacks & potential improvements in material quality for future CMOS applications            |    |

|    | Defect reduction in directed self-assembly processes                                                                                             | 23 |

|    | Transmission electron microscopy: more than an image                                                                                             | 23 |

|    | 3D chemical analysis of microelectronics systems                                                                                                 | 24 |

|    | Compositional inaccuracies in laser-assisted atom probe tomography: the case of B-doped SiGe                                                     | 25 |

|    | Fabrication and evaluation of diamond tips and probes for 3D nanoscale measurements                                                              | 26 |

|    | Detector arrays bringing novel capabilities to Rutherford backscattering spectrometry                                                            | 26 |

|    | Adaptive control of an accelerator based measurement system                                                                                      | 27 |

|    | Development of NV-diamond tip sensor with electrical readout                                                                                     |    |

|    | Composition measurements in advanced III-V nanostructures using Raman spectroscopy                                                               |    |

|    | Electrical SPM characterization of 2D semiconductors                                                                                             | 29 |

|      | Electrical SPM for 3D carrier quantification                                                                           | 29 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

|      | Predicting dielectric breakdown voltage in MOSFETs: the missing link?                                                  | 30 |

|      | Controlled transfer of two dimensional material                                                                        | 31 |

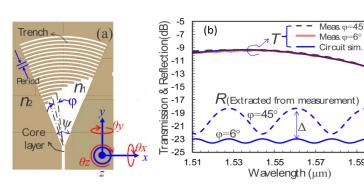

|      | High performance photonic grating couplers leveraging the small critical dimensions possible with advanced lithography | 31 |

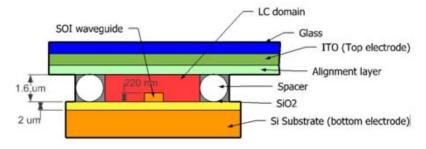

|      | Development of a liquid crystal-based phase shifter for the SiN photonics platform                                     | 33 |

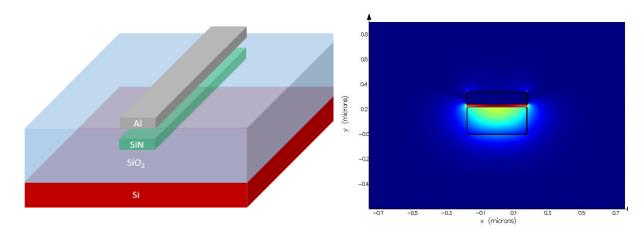

|      | Hybrid plasmonic-photonic devices for silicon nitride integrated circuits                                              | 33 |

|      | Electrochemical deposition of CuNi alloys for chip microbump technology                                                | 34 |

|      | Ge(Si) multi quantum well based optoelectronic devices                                                                 | 35 |

|      | Study of the kinetics of chemical reactions in nano-confined volumes                                                   | 35 |

|      | Explore process capabilities of state of the art etch reactors for advance device patterning                           | 36 |

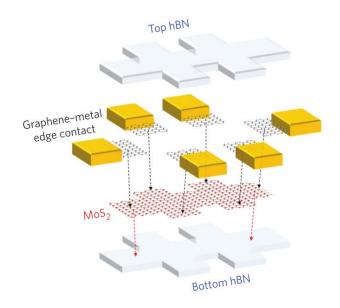

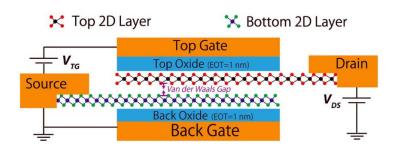

|      | Experimental study of MOSFETs and TFETs with 2D flake materials                                                        | 37 |

| II.  | Image Sensors and Vision Systems                                                                                       | 40 |

| III. | Silicon Photonics                                                                                                      | 41 |

|      | Investigation of CI based species on maximal dopand concentration of group IV epitaxial layers                         | 41 |

|      | Silicon photonics static process control and report automation                                                         | 41 |

| IV.  | Thin-Film Flexible Electronics                                                                                         | 43 |

|      | 3D TFT-based combined circuit and architecture exploration for cost and energy                                         | 43 |

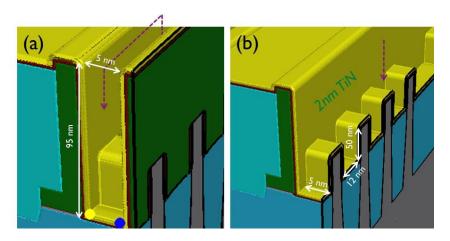

|      | Vertical channel oxide TFTs for low power and small foot-print device applications                                     | 43 |

|      | High-k gate dielectrics (HfO2 & Al2O3) to boost the performance of a-IGZO thin-film transistors                        | 44 |

|      | PZT sol-gel process development on large area substrate for piezoelectric actuators                                    | 44 |

|      | Stack optimization of infrared thin-film photodetectors                                                                | 45 |

|      | Low-temperature polysilicon TFT virtual design library                                                                 | 46 |

|      | Design and characterization of in-panel charge-sense amplifier for sensor array readout                                | 46 |

|      | Research of ESD protection for the TFT technology                                                                      | 47 |

| ٧.   | Life Sciences                                                                                                          | 48 |

|      | Nano-scale field effect transistor for biomolecule sensing                                                             | 48 |

|      | Cell sorting and characterization for cancer cell therapy applications                                                 | 48 |

|      | Microfluidic controlled differentiation of stem cells on chip                                                          | 49 |

|      | CMOS-based transfection-on-chip with single-cell resolution for targeted CRISPR gene editing                           | 49 |

|      | Building a microfluidic network for multiplex DNA amplification                                                        | 50 |

|      | Photonic read out of waveguide integrated nanopores                                                                    | 50 |

|     | Simulation of nanopore transistors                                                                                | 51   |

|-----|-------------------------------------------------------------------------------------------------------------------|------|

|     | CMOS compatible nanopore field-effect transistors                                                                 | 52   |

|     | Ultrasound holography using tunable acoustic lens                                                                 | 52   |

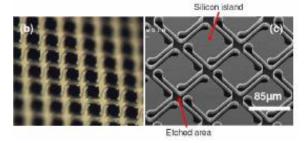

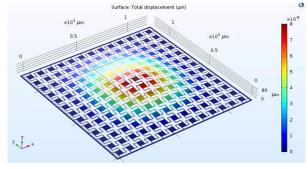

|     | Mechanical design of Kirigami structures for brain cell sensing                                                   | 53   |

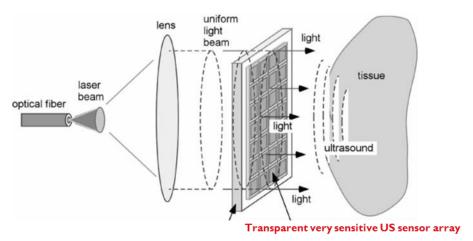

|     | PhotoAcoustic imaging set-up                                                                                      | 54   |

| VI. | . Wearables                                                                                                       | 55   |

|     | Interface circuits for physically unclonable functions                                                            | 55   |

|     | Unobtrusive measurement of capacitive electrocardiography (ECG) and bioimpedance (BIOZ) in automotive environment | 55   |

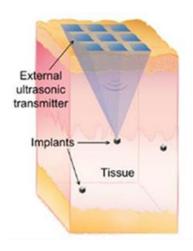

|     | Wireless power transfer for deep implants                                                                         | 56   |

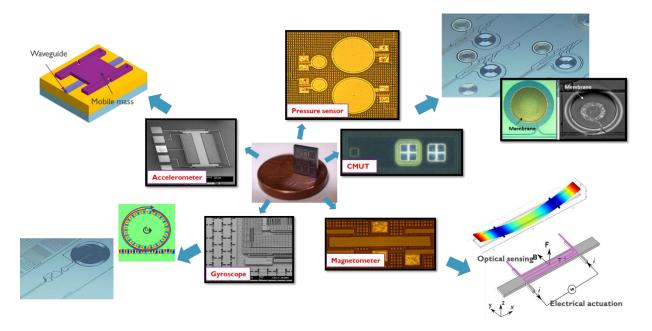

|     | Design of an optical IMU system                                                                                   | 56   |

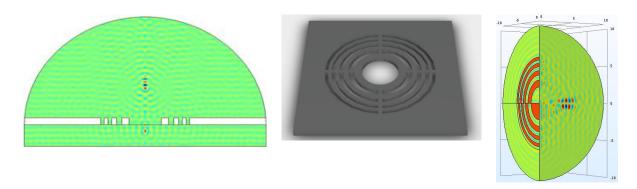

|     | Acoustic design for ultrasound power delivery for deep implant                                                    | 57   |

| ۷I  | I. Photovoltaics                                                                                                  | 59   |

|     | PCB design, realization and characterization of local DC-DC convertor for smart configurable PV modules           | 59   |

|     | Advanced thin film solar cell architectures                                                                       | 59   |

|     | Investigating the role of encapsulant adhesion on the reliability of a photovoltaic module                        | 60   |

|     | Fabrication and optoelectronic characterization of high band gap thin film solar cells                            | 61   |

|     | Characterization of poly-Si based passivated contacts                                                             | 61   |

|     | Investigation on reversible degradation of perovskite solar cells under light-darkness cycling                    | 62   |

|     | Defining optimal conditions for performance measurements of perovskite thin film PV modules                       | 63   |

|     | Understanding and overcoming instability in perovskite thin film PV modules                                       | 63   |

|     | Performance optimization of bifacial photovoltaic systems                                                         | 64   |

| ۷I  | II. GaN Power Electronics                                                                                         | 65   |

| ΙX  | . Wireless IoT Communication                                                                                      | 66   |

|     | Low-power ADC for radar sensing                                                                                   | 66   |

|     | Wideband mm-wave front-end circuits for 5G applications                                                           | 66   |

|     | Smart radars: machine learning for radar signals                                                                  | 67   |

| Χ.  | Solid State Batteries                                                                                             | 68   |

|     | Development and synthesis of dual electron and ion conductive materials for advanced Li-ion batteria              | es68 |

|    | Heterogeneous conductivity enhancement in solid state electrolytes for all-solid-state lithium ion batteries             | 68  |

|----|--------------------------------------------------------------------------------------------------------------------------|-----|

|    | Lithium alloys as reliable anode materials for Li-ion batteries                                                          | 69  |

|    | Modelling of a solid-composite electrolyte for Li-ion batteries                                                          | 69  |

| ΧI | . Data Science and Data Security                                                                                         | 7 I |

| ΧI | I. Process and Hardware Engineering                                                                                      | 72  |

|    | Automation of atomic force microscopy measurements                                                                       | 72  |

|    | Structural implementation of defectivity for QC                                                                          | 72  |

| ΧI | II. Software Engineering                                                                                                 | 74  |

| Χľ | V. Neuroelectronic Research (NERF)                                                                                       | 75  |

|    | Unraveling neuronal activity during locomotion                                                                           | 75  |

|    | Using machine learning and deep neural networks to automatically identify components of neural circuin the visual system |     |

|    | Using virtual reality to study the function and neural circuits in the mouse visual system                               | 76  |

|    | Understanding memory through real-time processing and closed-loop manipulation of brain activity                         | 76  |

|    | Engineering new devices and tools to study how the brain processes and stores information                                | 77  |

| X۷ | /. Microelectronics Design                                                                                               | 78  |

|    | Development of RadHard SAR ADC in 65nm CMOS                                                                              | 78  |

|    | Enhancements for RadHard IP in 180nm and 65nm CMOS                                                                       | 78  |

#### Information

Students from universities and engineering schools can apply for a Master thesis and/or internship project at imec. Imec offers topics in engineering (technology) and sciences in different fields of research.

All Master internship and thesis projects currently available at imec are collected in this topic guide. The projects are classified according to the imec expertises. You can find more detailed information on each expertise on <a href="https://www.imec-int.com">www.imec-int.com</a>. In addition, in this catalogue you will find the projects available with <a href="mailto:imec.IC-link">imec.IC-link</a> and NERF (www.nerf.be)

### How to apply?

Send an application email including your motivation letter and detailed resume to the responsible scientist(s) mentioned at the bottom of the topic description you choose.

The researcher(s) will screen your application and let you know whether or not you are selected for a project at imec.

It is not recommended to apply for more than three topics.

There is no application deadline. We accept applications at any time and deal with them throughout the year.

Master internship students usually receive an allowance. However, some research groups only accept self-supporting students. Do you want to know upfront whether the project you wish to apply for provides financial support? When sending in your application email then check the remuneration details with the responsible scientist. For some projects, it is already mentioned in the project description that an allowance will not be provided.

For more information, go to the Master thesis & internship section on the Work at imec tab on www.imec.be. Do you have additional questions, then send an email to <a href="mailto:student@imec.be">student@imec.be</a>.

For Master thesis/internship projects in **imec the Netherlands** refer to http://www.holstcentre.com/careers/thesis-opportunities or contact talent@imec-nl.nl.

#### After acceptance

In case of acceptance to our internship program you are bound to embark on a very exciting and interesting experience! For imec, your contribution as a student will be essential in meeting the deliverables in our programs. Therefore, it is vital that - once you accept to come to imec - we can count on your commitment and dedication for the entire duration of the internship period.

# I. CMOS & beyond CMOS

# Machine learning based computational lithography

As the chip scaling continues with the technology nodes to follow Moore's law, computational jobs such as optical proximity correction (OPC) and design-for-manufacturability (DFM) have become too intensive to carry out with introduction of more design data and models (mask, optical, resist, etch, topography-aware and CMP) to improve chip printability and prediction accuracy. 'Big Data' usually refers to data volumes that are so large that traditional data processing applications are inadequate, which exactly represents current OPC and DFM confront. In consequence, increased risk with increased ramp-up time from the research to the high volume manufacturing has been pointed out as risk. The student will use Machine Learning to apply the learning into computational lithography field that includes OPC and DFM. The student will learn conventional OPC and DFM flow, and work toward R&D in application of Machine learning into OPC and DFM flow with goals of 1) development of new algorithm, 2) reduction in number of computational iteration, and 3) optimization/minimization of DOE to shorten turn-around-time (TAT) in Semiconductor manufacturing. Machine learning and optimization may include study of a. Pattern recognition, b. Pattern extraction, c. Classification in Machine learning Modeling. Optimization incorporates mathematical and statistical concepts (effect, global/local min. search algorithm), or a new concept.

Type of project: Internship or thesis project, or combination of both

**Duration:** 6 months

<u>Degree:</u> Master in Engineering Technology or Master in Science or Master in Engineering majoring in computer science, electrotechnics/electrical engineering, nanoscience & nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Ryan ryoung-han kim (Ryan.ryoung.han.kim@imec.be) and Jae Uk Lee (Jae.uk.lee@imec.be).

### Ferroelectric device electrical characterization

Ferroelectric hafnium oxide (HfO2) attracted a lot of interests since its discovery in 2007. Its scalability and CMOS compatibility are two advantages over conventional ferroelectric materials, favoring new device integration. Such material could enable the fabrication of low power devices in standalone semiconductor manufacturing facilities due to its scalability and CMOS compatibility. Already, a one-transistor ferroelectric field effect transistor embedded NVM has been implemented for low power application. This integration demonstrates the potential utilization of such material system for memory applications. Doped ferroelectric HfO2 Metal/Insulator/Metal capacitors have been widely studied for DRAM and FeFET applications. Silicon electrodes have not been discussed in much detail so far, though it provides an input for vertical ferroelectric FET (V-FeFET), based on Flash NAND architecture.

The existence of ferroelectric properties in HfO2 was discovered in 2007 by Böscke et al. using silicon as dopant in a planar Metal/Insulator/Metal (MIM) capacitor. The presence of a small amount of dopant, a capping layer and a thermal anneal facilitate the transformation of the monoclinic phase into a non-centrosymmetric orthorhombic phase which is the origin of this property. FE-HfO2 has been mainly studied with planar MIM capacitor. The use of polycrystalline silicon (poly-Si) as electrodes has been proposed for the first time by IMEC. Such study provides an important input for 3D applications, aiming at disrupting 3D NAND market.

As an intern in memory device team at imec, you will support state-of-the-art ferroelectric technology development by characterizing and understanding of semiconductor devices. During your internship, you will have the opportunity to work with device characterization, reliability and integration engineers. You will be challenged by working on a cutting-edge technology, aiming at an innovative device never reported before in literature. Successful candidates must have:

- Excellent communication skills, both oral and written

- Ability to independently adapt & learn with the outcome of a completed project

- Background in solid state physics and semiconductor processing

- Constitute a plus but not a requirement:

- Device characterization experience

- Experience in the operation and of semiconductor instrumentation including, but not limited to:

- o Parameter analyzers, SPA, SMU

- LCR meters

- Oscilloscopes

- Pulse & waveform generators

- Wafer probers

- Knowledgeable in a variety of software tools and operating systems, including but not limited to:

- Python

- o C/C++

- Unix/Linux

- Matlab/Octave

Type of work: 80% ferroelectric electrical characterization, 15% understanding, 5% literature

Type of project: Internship or thesis project

**Duration:** 6–9 months

<u>Degree:</u> Master majoring in electrotechnics/electrical engineering, physics, materials engineering, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Simone Lavizzari (simone.lavizzari@imec.be) and Jan Van Houdt (Jan.VanHoudt@imec.be).

## Selective low-k dielectric growth using metal nitride conversion approach

Developing next generation chips for logic computation remains based on dimensional scaling. However, at present we entered an era where scaling is not anymore applied to basic functional elements (transistor, interconnect circuitry) but to the logic cell as a whole. New cell geometries are investigated in order to gain space by compacting all logic elements closer each to the other. In this framework, self-aligned architectures using selective deposition concepts are essential building blocks. The principle of selective deposition is to be able to grow a few nanometers thick film (I to 10nm) on some specific locations of the substrate, and not on others. This is typically done using sacrificial passivants or blocking agents (self-assembled monolayers - SAMs) or doing specific surface treatments (plasma-based) to de-activate or activate specific areas of the substrate. Depending on the natures of the substrate and the selectively deposited films, one consider four challenges: metal-on-metal deposition (MoM), dielectric-onmetal deposition (DoM), metal-on-dielectric deposition (MoD) or dielectric-on-dielectric deposition (DoD). DoD is particularly challenging since the targeted dielectric constant (k-value) is below 3, which poses significant challenges for the composition and microstructure of the grown/deposited dielectric, which added to the selectivity requirements, make the overall deposition process challenging. In this work, we will focus on DoD. Instead of doing direct deposition of a low-k dielectric, we propose an alternative two-step scheme. In the first part, a high-k dielectric (metal nitride) is deposited, using a conventional Atomic Layer Deposition (ALD) method. In the second part, this high-k is converted to a low-k carbo-nitride, using high-T chemistry in controlled atmosphere. The goal of the internship/Ms work is to understand the details of this high-T conversion reaction as a function of temperature, nature of gaseous reactants, pressure in the conversion chamber, starting metal-nitride composition and thickness (linked to diffusion lengths for in-diffusion and out-diffusion of species). Criteria of evaluation will be: final thickness of formed low-k dielectric, roughness, dielectric constant, composition, chemical resistance. The selectivity of the conversion process will be checked towards metals relevant to the most advanced technology nodes (Cu, Ru). Once

a viable conversion process will be established, some patterned vehicle will be used, where the selective conversion will be tested on a substrate showing both dielectric and metallic surfaces. The student will be trained on relevant ovens and etch systems (300mm, 200mm, LAB depending on availability), on material characterization techniques such as spectroscopic ellipsometry, grazing-angle Fourier-transformed X-ray spectroscopy, X-ray reflection spectroscopy, atomic force microscopy, scanning electron microscopy, and will interface with the Materials Characterization & Analysis (MCA) group of imec for more complex physico-chemical characterization techniques (XPS, SIMS, RBS). The k-value extraction will be done using available techniques at imec (metal-dots for small samples and/or Hg probe for 300mm wafers). The student's activity will be embedded and be reported into a module meeting devoted to self-aligned deposition techniques.

Type of project: Internship or thesis project

Degree: Master in Science majoring in chemistry/chemical engineering, physics, materials engineering

#### Responsible scientist(s):

For further information or for application, please contact Jean-Francois de Marneffe (Jean-Francois.deMarneffe@imec.be).

# Impact of thermal budget on spin-orbit torque and SOT-MRAM performances

There is considerable interest in electrically controlling nano-magnets in order to develop non-volatile magnetic memories (MRAM) [1]. The microelectronics industry is facing major challenges related to the volatility of CMOS cache memory elements (usually SRAM and eDRAM). Due to decreasing devices size, leakage current in standby mode are now dominating the power dissipation of CMOS circuits. Furthermore, the increased density and reduction in die area lead to heat dissipation and reliability issues. Integration of non-volatility in memory hierarchy would solve these issues by incredibly minimizing static power consumption. MRAMs are among most credible candidates that are low power and fast enough to compete with SRAM and replace them at cache level. Most advanced MRAM devices are magnetic tunnel junctions (MTJ) that consist of two ferromagnetic layers separated by a very thin oxide barrier, one of the layer being the storage layer, the other is used as reference layer. Depending on the relative orientation of the magnetization of these two layers (parallel/ anti-parallel), the MTI cell will exhibit low/high resistance through the tunnel magneto-resistance effect (TMR), defining the reading state (0/1). The writing operation relies on either the Spin Transfer Torque (STT) [1], the transfer of spin angular momentum from the reference layer to the free layer, or the Spin-Orbit Torque (SOT) [2,3], due to the charge-spin conversion mediated by the spinorbit interaction. The SOT mechanism allows for decoupling the read and write operations using a novel 3-terminal geometry (figure I.a), enabling for robust deterministic magnetization reversal at sub-ns scale [4]. This project explores materials and devices for SOT-MRAM applications and aims at characterizing the impact of thermal annealing on SOT-MRAM stacks performances.

This work is part of the exploratory magnetic memory project of imec. It covers competences in the fundamentals of magnetism and spintronics as well as in the structural, magnetic, and transport properties of thin film materials. Below are the main task to be performed during this internship. It will mostly consist of magnetic and electrical characterization (60%), nano-fabrication (30%) and literature (10%).

- I. Characterization of the magnetic properties of trilayer stacks and full SOT-MTJ stacks as a function of annealing temperature for different SOT systems.

- 2. Fabrication of simplified SOT devices (using above tri-layers) in order to analyze the impact of thermal annealing on SOT amplitude and critical switching current density.

- 3. Characterization of 300mm integrated SOT-MTJ cells (figure 1) as a function of annealing temperature.

[1] C. Chappert et al., Nature Material (2007), [2] M. Miron et al., Nature (2011); [3] K. Garello et al., Nature Nanotech (2013); [4] K. Garello et al., Appl. Phys. Lett. (2014)

Type of project: Thesis or thesis with internship project

**Duration:** 6 months

Degree: Master in Engineering majoring in physics, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Kevin Garello (Kevin.garello@imec.be).

# Low temperature epitaxial growth of Ga doped SiGe for future device applications

Current downscaling of MOS devices goes together with modifications of the transistor device geometry, the implementation of new materials and the introduction of new device concepts. Planar devices have been replaced by FinFET structures and new designs such as Gate All Around FETs (GAA) are being considered to tackle future scaling issues. In parallel, Si has successfully been replaced by strained SiGe (or strained Ge) in high mobility channels as well as for the implementation of Source/Drain (S/D) stressors. The reduction in transistors' dimensions leads to a reduction in the S/D contact area and an increase in contact resistance, which limits device performance. New approaches are therefore required to significantly reduce contact resistance. This triggered the research community to assess the use of alternative dopants, like Ga for pMOS devices. Imec reported record-breaking values for S/D contact resistivity (<10e9 Ohm.cm2) on Ga-implanted Si0.4Ge0.6 layers. However, the reported processing scheme requires an unwanted high thermal budget (laser anneal) and does not provide the necessary doping profile conformality on patterned wafers. No literature reports about epitaxial growth of highly Ga-doped SiGe or Ge by means of CVD. Indeed, major challenges need be overcome such as: I) the low Ga solubility in Si which in turn leads to a risk for Ga precipitation and agglomeration and 2) the unwanted but expected carbon incorporation, as commercially available Ga process gases contain CxHy groups which may dissociate and/or incorporate during growth. Developing selective epitaxial growth schemes of S/D materials with higher active doping concentrations than currently available will enable the continuation of current transistor scaling. Within the frame of this internship, the candidate will generate fundamental understandings enabling the implementation of Ga-doped Ge and SiGe as S/D materials for FinFET and GAA devices. The main scientific goal of this project to understand the electrical and structural material properties of the grown materials. Particular attention will be given to the impact of defects (vacancies, Ga clusters...) and carbon incoporation on dopants activation. With respect to exploring Ga-doped Ge and SiGe as S/D materials, experimental studies will be dedicated to the extraction of contact resistivity values by means of Circular Transmission Line Measurements (CTLM).

Type of project: Thesis with internship project

<u>Degree:</u> Master in Science or Master in Engineering majoring in physics, nanoscience & nanotechnology, materials engineering

#### Responsible scientist(s):

For further information or for application, please contact Clement Porret (Clement.Porret@imec.be) and Roger Loo (roger.loo@imec.be).

# Study of an optical metrology technique for advanced semiconductor process control

Device-dimension scaling is driving the industry towards ever tighter process specifications. A key research project in the area of Advanced Patterning involves the study of an alternative metrology technique for process control at the 7 nm and 5 nm nodes. Existing in-line metrology solutions are not suited to the extensive sampling required or depend on the time-consuming validation of complex physical reconstruction models. To address the need for more efficient and cost-effective metrology, Imec recently developed and patented the Pattern Shift Response (PSR) technique: an optical solution based on asymmetric marks designed to enhance placement sensitivity to patterning variation. PSR metrology applies to lithography and throughout subsequent steps of device fabrication. To enable

deployment for semiconductor manufacturing, fundamental characteristics of PSR need to be further explored and understood.

The project entails measuring PSR asymmetric mark design variations that have been implemented on imec masks, and evaluating their efficacy using metrics such as precision, repeatability, S/N etc. to quantify their metrology capability dependence on design dimensions and some acquisition settings. On the one hand, design variations include pitch, asymmetrical pattern and reference pattern dimensions etc.; on the other hand, scaling of the acquisition zone needs to be assessed.

The marks are patterned on 300mm wafers under representative process conditions, including both DUV and EUV exposures, and measured using a high performance automated optical microscope (KLA-Tencor ARCHER 500). After training, the student will collaborate with the supervisor and the team members to design experiments, pattern wafers, create recipes, perform measurements, analyze data and develop predictive models. The overall goal is to characterize the PSR mark design space. Based on results, the student will have the opportunity to propose and implement improvements to PSR metrology and process control methods.

A good knowledge of written and spoken English is necessary for this application. The student's academic background ranges physics, optics, semiconductor technology or related engineering fields and the student shows motivation with respect to R&D in the semiconductor industry. Knowledge of automation for big data analysis will be valued in the application process (e.g. python, matlab, excel macros).

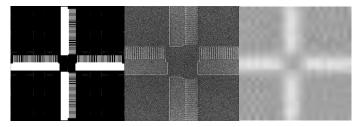

From left to right: Design, SEM picture and Optical microscope pictures of a type of asymmetrical PSR target.

More info about imec and the Advanced Patterning department:

https://www.imec-int.com/en/about-us

https://www.imec-int.com/en/advanced-patterning-and-key-process-steps

Type of project: Thesis or internship project, or combination of both

<u>Degree:</u> Master in Engineering Technology or Master in Science or Master in Engineering majoring in physics, nanoscience & nanotechnology, materials engineering

### Responsible scientist(s):

For further information or for application, please contact Vincent Truffert (vincent.truffert@imec.be), Patrick Wong (Patrick.Wong@imec.be) and Kit Ausschnitt (Kit.Ausschnitt.ext@imec.be).

### Spin wave-like excitations in low-dimensional ferromagnets

Integrated Circuits (ICs) are present in all electronic devices around us. In an effort to make these devices faster and cheaper, the smallest IC building blocks need to be scaled down. This further downscaling of transistors based on CMOS technology results however in a higher heat dissipation. An alternative for today's transistors is the spin wave majority gate, which is expected to have a low power dissipation when miniaturized. Genuine spin waves originate from deviations of individual, single spins with respect to the perfectly ordered ground state of a ferromagnet in which all spins are aligned parallel to each other. The waves that are propagating such deviations through the lattice of the ferromagnet are called spin waves and, as such, they can be excited only at very low temperatures. However, at room temperature one may excite similar waves, corresponding to the spatial variation of the macroscopic

magnetization vector that locally deviates from the spontaneous magnetization. Although the basic quantum theory of ferromagnetism has been established already in the previous century, various fundamental problems are left unsolved or remain to be highly controversial, especially those concerning low-dimensional magnets. Rather than relying on semi-classical theories and simulation programs, this project will focus on the fundamental physics of the spin dynamics of two-dimensional ferromagnets.

More specifically, this project addresses the time-dependent evolution of the magnetization and related quantities in order to mimic the propagation of the basic excitations and/or magnetization waves through low-dimensional magnets, such as spin wave buses or other (ultra)thin magnetic layers. Aiming at a full quantum dynamical treatment of low-dimensional spin systems, this project involves extensive computational effort, both numerically and on the theory side, where the shortcomings of commonly used classical dynamics based on the LLG equations need to be superseded. The questions that can be dealt with are: How does the local magnetization evolve in time and space? How to trigger the (phase-coherent?) propagation of elementary excitations (spin waves or spin wave-like deviations)? To which extent can we superimpose the propagation of magnetization waves, knowing that spin waves are no bosons and can therefore not be simply superimposed to generate all possible eigenstates? How detrimental is the effect of decoherence (spin-phonon interactions, spin-spin scattering...)?

Simulating the spin wave behavior in a spin wave majority gate is a very challenging task, due to its complex shape, multitude of interactions between different materials and the magnetic finite temperature excitations. Nevertheless, studying the ferromagnet at zero temperature using a simple geometry can provide already many of the desired insights. More specifically, the ferromagnet can be described as a saturated spin lattice with a Heisenberg spin Hamiltonian. Displacing some spins from their equilibrium orientation initiates a spin wave, whose dynamics is described using the Heisenberg equation of motion. The geometry itself can range from a finite spin chain up to an infinite two-dimensional lattice.

This project will involve both analytical and numerical calculations in the domains of quantum mechanics and magnetism.

Type of project: Thesis project

Degree: Master in Science or Master in Engineering majoring in physics, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Bart Sorée (bart.soree@imec.be), Wim Magnus (wim.magnus@imec.be) and Joren Vanherck (joren.vanherck@imec.be).

# Time-dependent Ginzburg-Landau simulations for superconducting rings

Quantum computing is a new paradigm that harnesses the full complexity of the quantum-mechanical wave function to solve a computational problem. Significant interest has been given to the field of quantum information and computation since the realization that certain algorithms, such as Shor's factoring algorithm, can in principal run exponentially faster on a quantum computer, compared to a classical computer. Analogous to their classical counterparts, the fundamental unit of a quantum computer is a quantum bit, typically referred to as a qubit. Qubits are two-level systems physically realized using spins (either nuclear or electronic), ion traps, photons, superconducting circuits, etc. At present, the major scalable platform for quantum computing employs superconducting qubits based on Josephson junctions, a superconductor interrupted by an insulating barrier.

The quantization of magnetic flux lies at the heart of prospective superconducting quantum bits. When a superconducting ring is placed in a magnetic field, the lowest energy state is achieved by inducing a current that expels the field from the bulk of the ring and ensures that the enclosed flux is an integer multiple of the flux quantum, a fundamental physical constant. Accordingly, a superconducting ring exhibits a discrete spectrum of trapped magnetic flux. Furthermore, the number of flux quanta trapped within the ring can only be changed by driving part or all of the ring into the normal state. Alternatively, by introducing a weak link in the ring, for instance a thin insulating barrier that forms a Josephson junction, the flux can tunnel in and out of the ring without destroying the superconducting state.

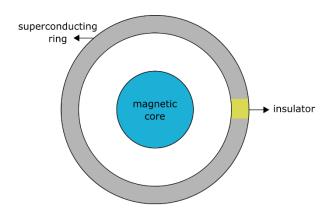

The goal of this project is to compare the dynamics of the flux transitions in a simple superconducting ring and in a ring interrupted by a Josephson junction, referred to as rf-SQUID. The time-dependent Ginzburg-Landau (GL)

equations will be solved numerically to model the transition of a superconducting ring between the integer flux states. The model under consideration (see figure below) is a superconducting ring (with and without the insulating barrier) pierced by a core, to which the magnetic field is confined. The research plan for this project starts by a theoretical study of superconductivity, the Josephson effect and the GL equations. Next, a numerical solution for the time-dependent GL equations is pursued for a superconducting ring and for the rf-SQUID.

Type of project: Thesis project

Degree: Master in Science majoring in physics, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Bart Sorée (bart.soree@imec.be), Wim Magnus (wim.magnus@imec.be) and Ahmed Kenawy (Ahmed.Kenawy@imec.be).

# **Modeling of Transmon Qubits**

Quantum supremacy, a term coined in 2012, is the prospect that quantum computers could solve problems that classical ones cannot by embracing the probabilistic nature of quantum mechanics. The tipping point at which quantum computers surpass classical ones is believed to be 49 quantum bits or qubits, the fundamental constituent of a quantum computer in analogy to classical bits. For this purpose, great efforts are exerted to scale up quantum computers in a race towards the first practical quantum computer.

At present, various physical realizations of quantum bits are pursued, most importantly superconducting qubits using Josephson junctions (a superconductor interrupted by an insulating barrier). Among the various implementations of superconducting qubits, the major scalable platform is currently the transmon qubit. The transmon is a variant of the charge qubit, a Josephson junction biased by a gate voltage, that operates at the regime of significantly increased ratio of Josephson energy and charging energy. As a consequence, transmons exhibit a substantial reduction in sensitivity to charge noise, while maintaining the anharmonic energy spectrum required to isolate the two-level system (TLS) defining the qubit. The noise insensitivity of transmons corresponds to a longer coherence time, i.e., the quantum state is preserved for a longer time to perform computations and to allow for error-correction.

The purpose of this project is to further improve the coherence time of transmons, a requirement for attaining highly-scalable quantum computers. The project primarily focuses on modeling transmons and the various noise sources responsible for dephasing and decoherence of the quantum state of the qubit (which can be viewed as a loss of information to the environment). Additionally, the research plan can be extended to account for the inter-qubit coupling (or, in other words, how transmons couple to each other) and how to enhance the coherence of the composite state of the overall system.

Type of project: Thesis project

Degree: Master in Science majoring in physics, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Bart Sorée (bart.soree@imec.be), Wim Magnus (wim.magnus@imec.be) and Ahmed Kenawy (Ahmed.Kenawy@imec.be).

# Cross-layer memory organisation simulation and exploration framework

At imec, we are developing a cross-layer simulator framework (entitled SEAT: System benchmarking for Enablement of Advanced Technologies) intended to exploring a wide variety of memory organisations/architectures and application domain targets with different characteristics. Until now, we have mainly worked on the cache hierarchy and main memory organisation. This endeavour was carried out in close cooperation with university groups, including LIRMM at Montpellier, France. With an eye towards the future, we would like to explore the extension of the memory organisation beyond the main memory. This will be particularly useful in evaluating the impact of emerging non-volatile memories like OxRAM, CBRAM, PCM at the storage class memory (SCM) level. For this purpose, the current simulator framework has to be further extended and validated with relevant academic/commercial benchmarks. The MSc thesis focus will be on this extension, and it will especially involve working on the software framework, system architecture and incorporation of the different non-volatile memory models. The activity will happen partly at imec, Leuven and partly at LIRMM, Montpellier, in close cooperation with the team of Prof. Lionel Torres and Prof. David Novo. So it will involve a stay outside Belgium.

Type of project: Thesis project

Duration: 6-9 months

Degree: Master in Engineering majoring in computer science, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Manu Komalan (perumkun@imec.be) and Francky Catthoor (catthoor@imec.be).

### Chemical mechanical polishing of new materials

Chemical mechanical polishing (CMP) has become a key step in microelectronic device fabrication: In the deposition step before CMP, an overburden of material is deposited to fill structures with metal material. During CMP, this overburden is removed, removing all metal from the field area while leaving the material inside the trenches untouched (no metal loss). In order to produce faster and more powerful commercial microprocessors, 'new' challenging materials such as copper, ruthenium, cobalt, manganese and their alloys need to be polished. For Cubarrier CMP for example, copper etching should be limited and galvanic corrosion between the copper and barrier materials needs to be minimized. In order to design a CMP process that can achieve this, the chemical reactions that occur between the materials and the CMP slurry need to be understood and controlled. The scope of this study is to develop a CMP process for the polishing of new materials and to gain a better understanding of the mechanisms that govern this CMP process. The polishing environment is mainly controlled by two factors: the specific materials to be polished and the CMP slurry. The type and combination of materials, the thickness as well as the deposition (e.g. chemical vapor deposition (CVD), physical vapor deposition (PVD), electroless deposition (ELD) or electroplating) and annealing method can be crucial in determining CMP performance. A (metal) CMP slurry uses oxidizers, complexating agents, inhibitors and pH adjusters to achieve a fine balance of chemical reactions that remove material at the surface while keeping corrosion under control by passivating the newly exposed surface during polishing. In this project the effect of various slurry components will be studied both during polishing on our experimental polisher and in a static slurry solution in a lab environment. Surface analysis techniques like X-ray spectroscopy (XPS), X-ray diffraction (XRD) and nano-indentation will provide the necessary extra information to understand which reactions and species are dominant at the surface. The analysis of the data will provide the understanding needed to design a model slurry which polishes the material away at a decent rate while achieving a good quality surface. If the model slurry design experiments are successful, the efficiency of the optimized slurry will be tested on blanket and/or patterned wafers to make sure that the CMP process removes the required materials with no defectivity or dishing/erosion issues. For this analysis techniques like high resolution profilometry (HRP), defectivity analysis, resistivity and ellipsometry, scanning electron microscopy (SEM) and atomic force microscopy (AFM) can be used.

Type of project: Thesis or internship project, or combination of both

**Duration: 3 months**

Degree: Master majoring in chemistry/chemical engineering, materials engineering, nanoscience & nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Lieve Teugels (teugels@imec.be).

# Photoresist line edge roughness and smoothing techniques in EUV lithography

Photolithography, the process used to fabricate integrated circuits, is the key enabler and driver for the semiconductor industry for device scaling. The miniaturization of feature sizes has been achieved mainly by shortening the wavelength of exposure tools by evolutionary advances in nanolithography and in turn by similar advances in photoresist technology. Today the shortening wavelength trend is continuing with the aim of achieving Ix nm resolution by the deployment of the extreme ultraviolet lithography (EUVL) using exposure light wavelength of I3.5 nm.

Current EUV photoresist platforms have performance limitations in resolution, line edge roughness (LER) and sensitivity (RLS). LER is currently of particular interest, as nearly all resists are currently not able to meet the LER target, especially if they have to meet resolution and sensitivity target simultaneously. Furthermore, it seems that the LER does not continue to shrink down with the resolution scaling, so post processing resist treatments are needed to smooth the resist.

In this frame, the student will produce own patterned resist samples on a full field EUV scanner, he will characterize the resist roughness with the use of scanning electron microscope (CDSEM) and dedicated software for the power density spectrum (PSD) analysis. He will understand the limits from a material chemistry standpoint and will test and benchmark post processing approaches (rinse, light curing, thermal annealing, solvent annealing) of multiple patterned resists with the EUV light aiming to finally assess all the techniques taken under examination. The student will work in the international research facility of imec interacting with multiple equipment and material partners.

To accomplish his task, the student has to have, besides a chemistry or nano-technology or materials science background, basic knowledge on statistics and have liking for the design of experiments, their execution (on equipment in labs or in cleanroom) and data analysis.

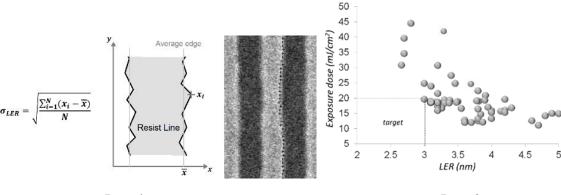

Figure 1 Figure 2

Figure 1: LER is a measure of the variability of the pattern. Mathematically, LER for a line and space pattern, is defined as the standard deviation from the average edge for every measurement point.

Figure 2: The experimental relationship between exposure dose and LER is reported for the case of 22nm dense line-space patterning. As the exposure dose decreases the LER values get worse and it is challenging to find resists that have sensitivity and roughness both in target.

Type of project: Thesis or internship project

**Duration:** 9 months

<u>Degree:</u> Master in Engineering Technology or Master in Science or Master in Engineering majoring in chemistry/chemical engineering, materials engineering, nanoscience & nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Danilo de Simone (danilo.desimone@imec.be), Geert Vandenberghe (Geert.Vandenberghe@imec.be) and Stefan de Gendt (Stefan.DeGendt@imec.be).

# Light-matter interaction in organic and inorganic photoresists for EUV lithography

Extreme ultraviolet lithography (EUVL) is the candidate to scaling down of semiconductor devices beyond the 1x nm technology node.

To realize the required EUVL targets the photoresist play a significant role and more intimate light-matter interaction studies (i.e. absorption, photo emission yield, electron efficiency, electron energy distribution of secondary electrons,...) are needed to get more fundamental understanding in their mechanism of interaction at 91.6eV (13.5nm wavelength).

In this frame, the student will work interacting with two different international research facilities.

At imec, in collaboration with material suppliers, for the design of the experiments (material selection and sample preparation), resist exposure on EUV full field scanner and data analysis.

At IOM-CNR Institute (Trieste, Italy) in collaboration with the group that is leading the CNR synchrotron beamline BEAR (http://www.elettra.trieste.it/elettra-beamlines/bear.html) at Elettra (Trieste, Italy) for the EUV-soft X-ray materials investigation and characterization including in particular photo absorption (XAS) and photoemission (UPS/XPS) spectroscopies.

This work will significantly contribute to the understanding of how different materials interact with the light and will lead to help the design of new photoresists for EUV lithography.

To accomplish his task, the student has to have fundamental understandings of x-ray, soft x-ray physics and radiation chemistry.

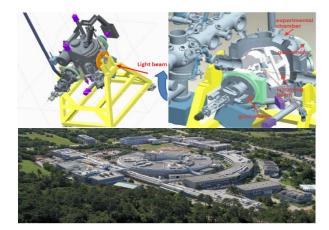

imec 300mm cleanroom and ASML NXE:3300 EUV tool

BEAR beamline at Elettra synchrotron facility

Type of project: Internship project

**Duration:** 9 months

<u>Degree:</u> Master in Engineering Technology or Master in Science or Master in Engineering majoring in chemistry/chemical engineering, materials engineering, nanoscience & nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Danilo de Simone (danilo.desimone@imec.be), Geert Vandenberghe (Geert.Vandenberghe@imec.be) and Stefan de Gendt (Stefan.DeGendt@imec.be).

### Simulations for semiconductor quantum dots

Progress in nanoscale fabrication techniques has allowed ever-smaller structures with increasing control. One fascinating result is the fabrication of quantum dots, structures where confinement is so strong that the system (at cryogenic temperatures) behaves as an artificial atom. Electrons can be loaded on to these dots one-by-one making them perfectly suited for the investigation of quantum effects. As such they're getting increasing attention in recent years due to their promising use as scalable unit blocks ('qubits') for future quantum computers.

This topic would focus on the simulation of quantum dots formed in semiconductor materials and voltage potentials applied by local gates. The student will investigate and simulate the most appropriate physical model to capture the interactions between the few electrons in the quantum dot and its environment. Different gate configurations are to be compared. Imec has a dedicated group for semiconductor simulations and the inhouse expertise would be available as an aid to the student.

We are looking for a motivated student with an interest in solid state physics and who's not afraid of some computer coding.

Type of project: Thesis project

Degree: Master in Science majoring in nanoscience & nanotechnology, physics

### Responsible scientist(s):

For further information or for application, please contact Bart Soree (Bart.Soree@imec.be), Nard Dumoulin (Nard.Dumoulin@imec.be) and Ahmed Kenawy (Ahmed.Kenawy@imec.be).

# Novel spin-on method to deposit self-assembled monolayers and thin polymeric films for surface and interface engineering in nano-IC applications

As the total transistors and interconnects sizes come down to few tens of nanometers and below, a shift in paradigm for the manufacture and integration of microelectronics components becomes apparent. Organic molecules - owing to their size, mechanical flexibility and chemical tunability - fit well in this slot and, thus, are expected to play a key role in IC downscaling. In this respect, self-assembled monolayers (SAMs) seem the best candidates. SAMs are a prototypical form of nanotechnology: the SAM precursor molecules carry the "instructions" required to generate an ordered, nanostructured material without external intervention. SAMs demonstrate that molecular-scale design, synthesis, and organization can generate macroscopic materials properties and functions. Although the details of the thermodynamics, kinetics, and mechanisms of assembly will differ significantly, these monomolecular films establish a model for developing general strategies to fabricate nanostructured materials from individual nanometer-scale components. Because SAMs can assemble onto surfaces of any geometry or size, they provide a general and highly flexible method to tailor the interfaces between nanometer-scale structures and their environment with molecular (i.e., subnanometer scale) precision. SAMs and polymeric films can control the wettability and electrostatic nature of the interfaces of individual nanostructures and thus their ability to organize into large assemblies and interact with overlayers adding chemical functionality, thermodynamic stability. While deposition on SAMs by dipping is already being extensively studied, SAM spin-on from organic solvents is relatively unexplored. The first phase of this project will focus on the deposition and characterization (water contact angle, FTIR, XPS, AFM, ..) of SAMs and eventually functionalized polymeric films on metal surfaces by spin-on from organic solvents. The study includes metal surface preparation before SAM deposition and the impact of post-SAM treatments such as anneal, gas flow and/or wet chemistries. The final aim of this work is to achieve a dense, ordered and defect-free SAM. In the second phase of the project we will focus on the scale-up of the SAM deposition process to 300mm wafers and on 300mm scale metrology techniques, such as light scattering, AFM, ellypsometry, mass measurement.

Type of project: Internship or thesis project, or combination of both

Duration: 6-12 months

<u>Degree:</u> Master in Engineering Technology or Master in Science or Master in Engineering majoring in chemistry/chemical engineering, materials engineering

#### Responsible scientist(s):

For further information or for application, please contact Silvia Armini (armini@imec.be).

# Fundamental study of SiCO, poly Si and SiO2 in Quasi-atomic layer etch mode

Progressively downscaling of CMOS Logic devices towards 7 nm node and beyond, requires highly accurate patterning processes (dry etch). The process flow is complex and the patterning steps require utmost precision because of the complex stacks of thin layers. Dry etch contrast is a key requirement for these thin layers: SiCO, Poly Si and SiO2. In this work, the student will focus on the in-depth understanding of the quasi atomic layer etch (Q-ALE) mechanism. In these dry etch processes, short gas injection cycles (radical fluxes) alternate with accurately controlled ion fluxes to target angstrom precision feature patterning. In this work, the student will focus on the in depth understanding of the etch mechanism. There will be a link with the area selective deposition research as controlled selective polymer deposition is a common goal in both fields.

The goal of the study should be bi-lateral:

1. The student will get an in-house training on etch tool operation and working in a 300 mm clean room according to the safety rules. He/she will get familiar with measurement tools like: thickness measurement (ellipsometry), mass measurements, TOFSIMS, XRR. Next to that, he/she will get a basic training/understanding of plasma etch as he/she will operate the etch tool fully independently. Our etch literature library will be available to help him/her understanding the etch processes and key parameters that control the process.

2. The student should gain insight in the etch mechanism and process window control of Q-ALE at the end of the internship. The idea is to study the plasma parameter space (pulsing, TCP power, bias power, gas nature, chuck temperature, Ar flow, ...) that affects the nature of the deposited CFx polymer and the etching of the blanket substrates. The best performing process conditions can be morphologically verified on relevant topography wafers. The practical work can be completed with a literature study on the specific etch plasma's. At the end of the internship all the results should be compiled in a scientific report.

Type of project: Thesis with internship project

**Duration:** 6 months

<u>Degree:</u> Master in Engineering Technology or Master in Science majoring in chemistry/chemical engineering, materials engineering, nanoscience/nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Efrain Altamirano Sanchez (Efrain.AltamiranoSanchez@imec.be) and Geert Mannaert (Geert.Mannaert@imec.be).

# Modeling of magnetoelectric coupling for advanced spintronic applications

Spintronics is a novel field of electronics that uses the spin of electrons or the magnetization of thin films instead of charge in memory or logic computation devices. A key issue of spintronics is the energy-efficient control of the magnetization in such devices. Current device concepts are often based on the control of the magnetization by currents, for example via generated magnetic fields or recently discovered effects, such as spin-transfer torque or spin-orbit torque. However, such techniques are typically not very energy-efficient and it would be very desirable to control the magnetization by electric fields instead. In principle, this can be done by the magnetoelectric effect, which couples electric fields to the magnetization. This effect is currently strongly considered to be included in future generations of low-power spintronic devices.

Magnetoelectric effects naturally occur in multiferroic materials but much stronger strain-induced magnetoelectric coupling can be observed in composite materials consisting of piezoelectric and magnetostrictive materials. The application in spintronic devices requires a detailed understanding of the effects of the geometry (e.g. the relative directions of the electric field and the magnetization) as well as thermal fluctuations on the magnetization dynamics. In this thesis, the student will perform micromagnetic simulations to study the magnetoelectric coupling in different geometries and different material systems. An important parameter will be the magnetocrystalline anisotropy of the magnet. The goal of the thesis is to develop efficient strategies to excite, control, and detect magnetization dynamics (including both magnetic switching as well as spin waves) by the magnetoelectric effect and transfer them to a magnetic waveguide. The work will be in close collaboration with experimentalists working on integration of magnetoelectrics into spintronic devices for beyond CMOS logic.

Type of project: Thesis project

Degree: Master in Science majoring in nanoscience/nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Christoph Adelmann (christoph.adelmann@imec.be), Florin Ciubotaru (florin.ciubotaru@imec.be) and Adrien Vaysset (adrien.vaysset@imec.be).

# Spintronic devices based on spin waves for beyond CMOS applications

Spintronic devices based on spin waves are promising alternatives to the CMOS technology and have high potential for power and area reduction per computing throughput. The information can be encoded in either the amplitude or the phase of the wave, while the logic operation is based on the interference of spin waves, which is a keystone for the realization of logic gates. To be competitive with actual CMOS technology the spin wave devices need to tackle waves with wavelengths below 100 nm and a miniaturization down to the nanoscale. Thus, the understanding of the properties of spin waves as their generation and propagation, the phase control and the interference mechanism at the nano-scale are of fundamental importance for the realization of the logic gates.

Within this thesis project, the student will fabricate spin-wave devices based on different magnetic materials, from micro- down to the nanoscale and will contribute to their characterization in the microwave frequency range leading to important properties as spin wave dispersion relation, their damping and their propagation characteristics in the linear and non-linear regimes, including a phase analysis. The results will be an important step to understand the emission, the routing and the combination/interference of spin waves to continue the assessment of the concept devices as alternatives or complements to CMOS transistors in future technology nodes. The experimental work will be performed in close collaboration with modeling activities (materials, devices, circuits) in the spintronics group at imec. The student should have a strong interest in nanofabrication in a cleanroom environment as well as in leading edge research topics on magnetism and magnetic materials.

Type of project: Thesis or internship project, or combination of both

**Duration:** 6 months

<u>Degree:</u> Master in Science or Master in Engineering majoring in nanoscience/nanotechnology, physics, electrotechnics/electrical engineering

#### Responsible scientist(s):

For further information or for application, please contact Christoph Adelmann (christoph.adelmann@imec.be), Florin Ciubotaru (florin.ciubotaru@imec.be) and Iuliana Radu (Iuliana.Radu@imec.be).

# Reliability assessment of RRAM memory devices

Memory devices based on resistive switching, the so-called Resistive Random Access Memory (RRAM), are currently considered as strong candidates for next-generation memory applications. The switching mechanism relies on the voltage-driven electrochemical formation/dissolution of a conductive filament in a solid electrolyte, leading to the commutation between a high-resistive state (HRS) and a low-resistive state (LRS) and vice versa. A typical RRAM device consists of an electrically insulator film, where the resistive switching occurs, sandwiched between two electrodes[1]. Promising features, such as scalability potential [2], fast and low-current operation, long-endurance lifetime, and good data retention[3-4], have already been reported for RRAM devices. However, the reduction of the operating power, which is crucial for aiming at Internet of Things (IoT) applications, induces a large increase in the state variability and a deterioration of the memory performances, hindering a massive introduction of this technology in the memory market. This internship will focus on the electrical characterization and reliability assessment of cutting-edge RRAM devices for low-power applications, to outline the impact of materials and integration schemes on the memory performance and to identify the root causes of reliability failures for proposing further improvement of the stacks. You will be trained in the use of advanced electrical characterization tools and you will carry out reliability assessment by using state-of-the-art characterization techniques, benchmarking different RRAM technologies. Careful and critical data analysis will be an essential part of the task, as well as proposing alternative characterization strategies for effective reliability assessment. You will work in a dynamic R&D environment and you will be expected to regularly present and discuss your results with a team of experts in the field. Therefore, a proficient use of English is also required. A good command of data analysis softwares (Matlab, Origin, etc.) will be considered a strong plus.

- [1] R. Waser et al., "Redox-Based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges", Advanced Materials, 21, 2632-2663 (2009)

- [2] B. Govoreanu et al., "10×10nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation", IEDM Tech. Digest, 729-732 (2011)

- [2] S. Sills et al., "Challenges for High-Density 16Gb ReRAM with 27nm Technology", VLSI Tech. Digest, T106 (2015)

- [3] A. Belmonte et al., "A Thermally Stable and High-Performance 90-nm Al2O3\Cu-Based 1T1R CBRAM Cell", Trans. On El. Devices, 60 (11), 3690-3695 (2013)

Type of project: Thesis or internship project, or combination of both

**Duration:** minimum 3 months

<u>Degree:</u> Master in Science or Master in Engineering majoring in nanoscience/nanotechnology, physics, electrotechnics/electrical engineering

#### Responsible scientist(s):

For further information or for application, please contact Attilio Belmonte (attilio.belmonte@imec.be) and Andrea Fantini (andrea.fantini@imec.be).

# Magnetism in graphene for spin-orbit torque (SOT) devices

Magnetic random access memories (MRAM) are foreseen to be the most credible non-volatile memories, which are low power, high endurance and fast enough to compete with cache CMOS elements. So far, spin transfer torque (STT) is the mature mechanism used to write magnetic tunnel junction (MTJ) which are at the core of MRAM bit cells, however, there is a need for exploring new concepts and new material systems to overcome STT-MRAM limitations. Meanwhile, strong effort has been devoted on creating and manipulating magnetism in two-dimensional graphene layer and its further implementation in spintronic-based MRAM devices. Graphene has already shown the possibility to propagate spins over a very long distances [1,2]. However, pristine graphene only exhibit Landau orbital diamagnetism, not yet suitable to use it as the magnetic bit for the memory element. There may be the possibility that the long range ferromagnetic ordering can be introduced in bybrid graphene non-ferromagnetic metals (diamagnetic Cu and paramagnetic Mn) by the mechanism based on magnetic hardening of the metal atoms [3]. Nevertheless, graphene allows to manipulate the magnetic anisotropy energy in existing ferromagnetic materials (Co) via the hybridization between the π-orbitals in graphene and the nearby spin-polarized d-orbitals in magnetic materials [4] that can help to reduce the material stack in the currently used MRAM. All these advanced and innovative concepts open up the path to novel graphene-based spintronic devices and the possibility to create and manipulate spin current through spin-orbit effects for future non-volatile MRAM application.

Imec has demonstrated in the past years the capacity to produce state of the art STT-MRAM. Furthermore, imec is currently developing methods for large scale growth and transfer of high quality 2D materials (graphene and others). Therefore, imec offers a unique possibility to bridge these two worlds for magnetic-memory related activities, in a FAB environment. Below are the main task to be performed during this internship part of the Exploratory magnetic memory project of imec. It will be mostly consist of graphene transfer (20%), nano-fabrication (40%), magnetic and electrical characterization (30%), and literature (10%).

- I. Different transfer methods of chemical vapour deposition grown graphene on SiO2 or on other given substrates.

- II. Fabrication of hybrid graphene-metal heterostructure Hall-bars and magnetic tunnel junctions (MTJs).

- III. Characterization of the magnetic properties and spin-orbit effect by measuring Hall effect and tunnel magnetoresistance (TMR).

[1] N. Tombros et al., Nature (2007), [2] S. Roche et al., 2D Materials (2015); [3] F. A. Ma'Mari et al., Nature (2015); [4] H. Yang et al., Nano Lett. (2016).

Type of project: Thesis project or thesis with internship project

**Duration:** 6 months

Degree: Master in Engineering majoring in nanoscience/nanotechnology, physics

#### Responsible scientist(s):

For further information or for application, please contact Kevin Garello (Kevin.garello@imec.be) and Subir Parui (Subir.Parui@imec.be).

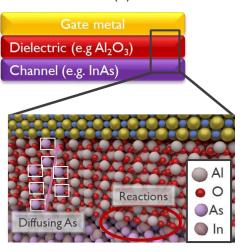

# Thermal degradation mechanisms in III/V - dielectric stacks & potential improvements in material quality for future CMOS applications

Computers, cellphones, etc. have seen a continues increase in performance and potential ever since they were invented centuries ago. We all take this as a given, and for many years it was, to increase performance the task was to shrink down the elementary building blocks so more could fit onto a given area. But this trend is coming to a halt as it is getting harder and harder to go smaller. So now, new strategies are needed to allow the performance of these appliances to keep increasing are needed. One of these strategies consist of introducing new materials and treatments and has already shown great potential.

In this project, you will work on a promising class of semiconductors know as III-V alloys. These materials promise a remarkable increase in performance and reduction in power which would make them candidates for everything from supercomputers to making your cellphone consume less. Of course no innovation comes without its challenges, for III-V this challenge lies in a lower thermal stability than the current material of choice (Si).

Consider the two elementary components found in transistors, namely the (III-V) channel (through which the current flows) and the dielectric (which allows isolates gate and channel and allows the buildup of an electric field). This dielectric generally has a lot of structural defects that need to be cured by applying temperature. However, combining that with a thermally unstable channel is no easy task. The goal of this project is thus to come to a deeper understanding of the mechanisms at play in this III-V/dielectric stack as temperature increases. What trend does the curing of the dielectric follow with temperature? At what point will the III-V material start to destabilize and diffuse through the dielectric, at what rate? Could we potentially find a dielectric that acts as a diffusion barrier thus allowing higher temperatures to be achieved?

These are all interesting questions, answering of which will bring help realize faster and more reliable devices for the future.

As part of the project the student will investigate the mechanisms at play at different temperatures (diffusion, reactions, intermixing, ...). To do this samples of III-V materials capped with several dielectrics are available which can be given a thermal budget (temperature ,time, atmosphere(N2 vs H2,...) and analyzed using the many chemical/physical characterization techniques available on the IMEC site. The starting point of this project will be the knowledge base already gathered on thermal stability of these materials in the research group.

All trainings (techniques, tools,...) will be provided as part of the thesis.

Type of project: Thesis project

Degree: Master majoring in chemistry/chemical engineering, materials engineering, nanoscience/nanotechnology

#### Responsible scientist(s):

For further information or for application, please contact Dieter Claes (Dieter.Claes@imec.be).

# Defect reduction in directed self-assembly processes