# GaN-ICs FOR MONOLITHIC INTEGRATION OF POWER SYSTEMS

To unlock the full potential of GaN power electronics, imec offers a unique GaN-on-SOI process. The deep-trench isolation implemented in this process provides full isolation between power devices, drivers, control and protection circuits. This, in turn, enables the manufacturing of complex GaN ICs. In addition to accommodating smaller form factors, the close proximity of devices drastically reduces parasitic inductance, resulting in a significant switching speed enhancement.

#### **LOW-COST MPW AND DEDICATED MASK RUNS**

To make GaN-on-SOI devices and circuits more affordable and easily available to its customers, imec offers a Multi-Project Wafer (MPW) service. In this MPW model, mask, processing and engineering costs are shared across multiple customer designs, typically delivering prototyping runs of 20 samples dies. For even larger quantities, dedicated mask runs can also be requested which return approximately 12 x 200 mm/8 inch wafers. For even larger productions runs, we offer the possibility of engaging with external manufacturing partners.

## STATE-OF-THE-ART ENHANCEMENT MODE POWER DEVICES ON 200mm/8-INCH Si WAFER

Today, GaN-based power devices are mainly available as discrete components which have, nonetheless, been used to push both operating frequencies and efficiencies of Switched-Mode Power Supplies (SMPS) to record levels. The technology's full potential, however, has been difficult to unlock due to difficulties in reducing the parasitic inductances, the necessity of extremely fast turn-on times, and the low Cg/Cgd ratio. Solutions using discrete GaN power devices have therefore resulted in maximum switching speeds far short of their potential values.

Imec's GaN-on-SOIIC technology circumvents these limitations by allowing customers to monolithically integrate components such as half-bridge and GaN drivers onto the same die, minimizing parasitic inductance.

### WITH IMEC'S GaN-IC TECHNOLOGY YOU ARE ABLE TO:

- Integrate multiple transistors on a single IC using trench isolation

- Save package cost by packaging one instead of multiple devices

- Reduce system parasitic inductance

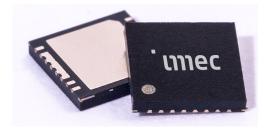

Picture of the 5x5mm² 200V 15A packaged GaN device

### **GaN-ON-SOI DESIGN KIT**

To make this technology more easily available, imec provides an extensive GaN-on-SOI Process Design Kit (PDK). This kit includes process documentation, library devices, layout guidelines for custom design, verification and models. Low-ohmic and high-ohmic resistors are provided, as well as Metal/Oxide/Metal capacitors, temperature sensors and low voltage logic devices and logic gates (invertors, NAND, NOR, RS Flip-flops,...). These enable customers to design highly integrated GaN power systems on chip. The PDK is available after signing imec's GaN-IC Design Kit License Agreement (DKLA).

### 200 V e-MODE p-GaN HEMT

Datasheet Power Device with Weff = 36 mm

| SYMBOL                       | DESCRIPTION                     | TEST CONDITIONS                                     | MIN | TYP  | MAX | UNIT |

|------------------------------|---------------------------------|-----------------------------------------------------|-----|------|-----|------|

| ABSOLUTE MAXIMUM RATINGS     |                                 |                                                     |     |      |     |      |

| BV <sub>DS</sub>             | Drain-Source voltage            |                                                     |     |      | 200 | ٧    |

| I <sub>D</sub>               | Pulsed Drain current            | 1 ms pulse                                          |     |      | 10  | А    |

| V <sub>GS</sub>              | Gate-Source voltage             |                                                     |     |      | 7   | ٧    |

| ON/OFF STATE CHARACTERISTICS |                                 |                                                     |     |      |     |      |

| BV <sub>DS</sub>             | Drain-Source voltage            | $V_{GS} = 0 \text{ V}, I_{D} = 1 \mu\text{A/mm}$    | 200 |      |     | ٧    |

| I <sub>DSS</sub>             | Drain-Source leakage            | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 200 V      |     | 0.5  |     | μА   |

| I <sub>GSS</sub>             | Gate-Source leakage             | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 200 V      |     | 0.27 |     | μΑ   |

| R <sub>DS-ON</sub>           | Drain-Source ON resistance      | $V_{GS} = 7 \text{ V}, I_{D} = 2 \text{ A}$         |     | 0.16 |     | Ω    |

| V <sub>TH</sub>              | Gate-Source voltage             | maximum g <sub>m</sub>                              |     | 2.3  |     | · V  |

|                              |                                 | $V_{DS} = 0.1 \text{ V}, I_{D} = 10 \mu\text{A/mm}$ |     | 1.3  |     |      |

| DYNAMIC CHARACTERISTICS      |                                 |                                                     |     |      |     |      |

| C <sub>ISS</sub>             | Input capacitance               | V <sub>GS</sub> = 0 V                               |     | 55   |     | рF   |

| C <sub>OSS</sub>             | Output capacitance              | V <sub>DS</sub> = 200 V<br>f = 1 MHz                |     | 35   |     | pF   |

| C <sub>RSS</sub>             | Reverse transfer<br>capacitance | 1 111112                                            |     | 0.97 |     | рF   |

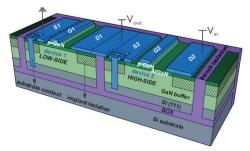

### MONOLITHIC INTEGRATION USING Gan-On-SOI

Except for systems at low voltage (<50Volt), cointegration of low-side and high-side power devices is not possible using GaN-on-Si substrates:

- The common Si substrate results in back-gating effects on the high-side power devices.

- The buried oxide of the SOI, the oxide-filled deep trenches and the deep Si contact effectively eliminate the back-gating effect.

Schematic cross-section of monolithically integrated half-bridge with enhancement mode low-side and high-side devices fabricated on 200 mm GaN-on-SOI with trench isolation.

### **DISCRETE COMPONENTS ON PCB**

### **INTEGRATED HALF BRIDGE AND DRIVER**

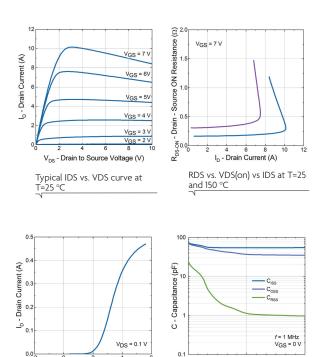

V<sub>DS</sub> - Drain to Source Voltage (V)

Typical CISS , COSS and CRSS vs VDS at T=25  $^{\circ}$ C Measurements on-wafer (no packaging parasitics included).

$V_{GS}$  - Gate to Source Voltage (V) Typical IDS vs. VGS curve at

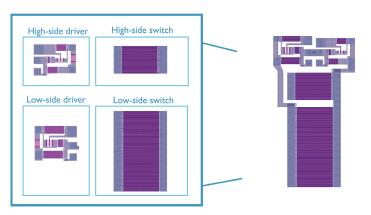

Monolithic integration of half-bridge and gate driver on imec's GaN IC platform.

To use the full potential of the fast switching speed of GaN power devices, the drivers should be co-integrated to lower the parasitic inductance.

Further functionality can be added through the low-voltage logic and analog switches, the high-ohmic and low-ohmic resistors and the integrated MIM-capacitors.

### **MPW RUNS**

Maritza Tangarife Ortiz ganmpw@imec-int.com +32 16 28 13 72

### **DEDICATED PROTOTYPE**

Denis Macron

Denis.Marcon@imec.be

+32 16 28 84 04

### **TECHNICAL QUESTIONS**

Stefaan Decoutere Stefaan.Decoutere@imec.be +32 16 28 15 03

DISCLAIMER - This information is provided 'AS IS', without any representation or warranty. Imec is a registered trademark for the activities of IMEC International (a legal entity set up under Belgian law as a "stichting van openbaar nut"), imec Belgium (IMEC vzw supported by the Flemish Government), imec the Netherlands (Stichting IMEC Nederland, part of Holst Centre which is supported by the Dutch Government), imec Taiwan (IMEC Taiwan Co.) and imec China (IMEC Microelectronics (Shanghai) Co. Ltd.) and imec India (Imec India Private Limited), imec Florida (IMEC USA nanoelectronics design center).