Simulating Dynamic Interaction Between Main Memory and Storage Technology

Master projects/internships - Leuven | More than two weeks ago

In order to improve today’s computing devices like smartphones, laptops and high-performance servers, researchers must face the so-called memory wall: It is the memory within these computers that limits overall performance and energy efficiency. Hence...

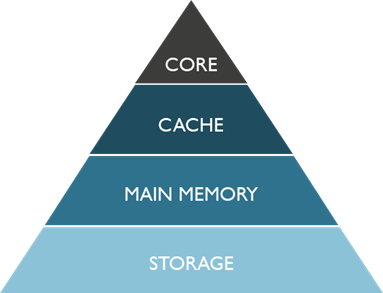

In order to improve today’s computing devices like smartphones, laptops and high-performance servers, researchers must face the so-called memory wall: It is the memory within these computers that limits overall performance and energy efficiency. Hence computer architects tried to solve this problem using a memory hierarchy: fast, small memories enable caching of data close the computing cores, while larger, slower memories provide the large capacity to store large amounts of data.

Aggressive technology scaling has exposed limitations of current memory and data storage technologies like SRAM, DRAM and Flash. Thus, several new emerging memory technologies are currently being investigated to eventually satisfy the need for continuously higher memory capacity and system performance, with lower energy consumption. One such an example is Phase Change memory (PCM), as Intel recently introduced with their 3D Xpoint Optane products. Each of these new technologies has properties of interest, such as high density and low power, but also inherent flaws, for example high latency. Hence, a strong need for cross-objective trade-off exploration is required to match the requirements for the different memory hierarchy layers.

To correctly capture the overall impact of such a new memory technology, we translate these characteristics to system-level impact using a memory system simulator. The high-level nature (C++, python) of these simulators enables flexible exploration of different memory technologies and architectures.

In this master thesis internship, the student will focus on the interaction of main memory and storage layers in the memory hierarchy of figure 1. The interaction between these two is traditionally orchestrated by the Operating System using the concept of virtual memory. The student will extend an existing main memory simulator (Ramulator) and combine it with a storage simulator (MQSim), to accurately capture this interaction, enabling fast exploration of alternative memory and storage technology. This activity will happen in cooperation with the team of Prof. Onur Mutlu in ETH Zurich.

Type of Project: Thesis

Master's degree: Master of Science

Duration: 6 to 9 months

Master program: Computer Science

Supervising scientist(s): For further information or for application, please contact Francky Catthoor (francky.catthoor@imec.be)

Imec allowance will be provided.