Design of readout and stimulation systems on flexible circuits for brain-disorder treatment

Leuven | More than two weeks ago

You will contribute to next-generation brain activity readout and stimulation circuits on ultra-thin flexible substrates

The implementation of low power and low noise low-temperature polycrystalline -Si (LTPS) TFT readout IC for brain-disorder treatment [1] on flexible substrates is targeted in this PhD topic. The PhD work will not only include the design but also precise analog (&noise) modeling and characterization of industrial LTPS-TFT technology. The readout IC would need to work with an array of multiple μm-range electrodes and adhere to speed/power and noise requirements to multiplex multiple sub-mV signals on the same line. By integrating readout electronics on the same substrate as the electrode array, further upscaling of the array is enabled, due to reduced connections, but also the total cost of the system is reduced. Moreover, up to 1000x larger area (of brain, tissue, etc) can be covered by large-area electronics (LAE) to enable broader studies of the human body. Conformal coverage of (brain) tissues and also lightweight, due to the very thin (<15μm) and flexible nature of the technology, can provide not only more input but also better signal-to-noise ratio and less invasive electronics.

First step would be to characterize and model the noise behavior of LTPS technology on thin flexible plastic substrates. Then, the design of a low-power and low-noise amplifier and multiplexer will be targeted. The frontend IC would need to meet below the state-of-art noise (<1μV/sqrt(hz)) levels but also to amplify the bio-signals up to 60dB by dissipating few tens of uW range of power. Noise shaping techniques should be applied to improve the performance of the readout IC and frontend amplifier and power reduction techniques to reduce the emitted heat from the chip critical for bio-applications.

Final step is to advance the readout IC by designing an ADC to digitize the amplified signals on the same flexible foil as the electrode array. Ideally, the input (amplified) signals will be in the tens of mV range which is below the Vt sigma of the technology. Vt compensation and offset cancellation techniques have to be explored to enable ADC operation and adequate resolution, depending on the application. At the same time, the speed requirement of hundred of Hz of bio-signals might be still an obstacle that will need to be traded off for the power and accuracy of the system.

[1] K. W. Scangos et al., “Closed-loop neuromodulation in an individual with treatment-resistant depression,” Nat Med 27 (10), Oct. 2021, doi: 10.1038/s41591-021-01480-w

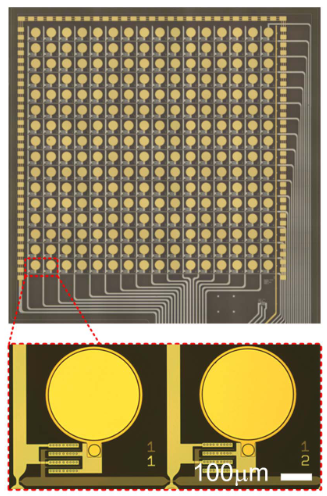

[2] Picture of ECoG array from: X. Huang et al., "Actively Multiplexed μECoG Brain Implant System With Incremental-ΔΣ ADCs Employing Bulk-DACs," in IEEE Journal of Solid-State Circuits, vol. 57, no. 11, pp. 3312-3323, Nov. 2022, doi: 10.1109/JSSC.2022.3201704

Required background: Analog circuit design, device modeling

Type of work: 60% design and simulation, 20% experimental, 10% modeling, 10% literature

Supervisor: Kris Myny

Co-supervisor: Nikolas Papadopoulos

Daily advisor: Nikolas Papadopoulos

The reference code for this position is 2024-144. Mention this reference code on your application form.