Hetero-integrated III-V Amplifiers on RF Silicon Interposer for Sub-THz Radar

PhD - Leuven | More than two weeks ago

Automotive radar technology in the 76 – 81 GHz band is well established. At these frequencies the output power of silicon-based technologies (Bulk Si / SiGe / Si Bipolar) is sufficient for most radar application scenarios. This is then combined with different types of packages and/or antennas for the type of radar in question. For short range radar PCB/planar antennas are used and for long range radars Waveguide antennas are used.

Next generation radars at 140 GHz aim to provide better resolution and smaller form factors. However, they also present several challenges:

- Everything else equal, there is a 5 dB penalty going from 79 to 140 GHz in the received power for the same range

- The output power of PAs and the noise figure of LNAs degrade significantly when going above 100 GHz for silicon technologies as the operating frequencies approach the cut-off frequency of the transistors

- Passive interconnect solutions based on PCBs incur excessively high loss and signal leakage due to material properties as well as large feature sizes

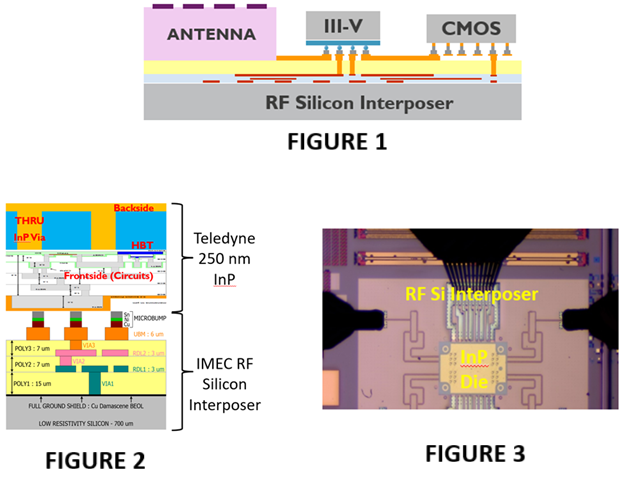

III-V technologies (InP / GaN) provide better efficiency and output power at higher frequencies and can overcome the challenges mentioned above (point 1 and 2). However, these technologies have a low level of maturity and high cost compared to their silicon counterparts. Furthermore, the entire radar system needs to be integrated into a package which minimizes RF loss (point 3). Finally, the chiplet approach common in digital systems needs to be adopted for RF systems. In this approach, only the final PA/LNA stages will be implemented in small sized III-V chiplets to keep costs down and the rest of the system will be implemented in Silicon technologies (FIGURE 1).

Waferscale Silicon interposer technology is a well-established interconnect solution for digital systems like microprocessors, high bandwidth memory and chip-to-chip communication. IMEC has developed a heterogeneous integration platform customized for MM-Wave and Sub-THz frequencies based on the digital interposer. It has several passive components optimized for RF applications:

- Transmission Lines on Low-Loss polymers with loss of 0.3 dB/mm at 140 GHz, 0.6 dB/mm at 220 GHz, 0.9 dB/mm at 325 GHz

- High Density MIMCAPs based on High-K Gate Dielectrics and 3D patterning with capacitance densities of 30 fF/um2

- Highly-scaled Micro-bumps with diameters of 15 um and pitch of 40 um for chip interconnects with minimal parasitics upto Sub-THz frequencies

In 2024, we assembled an InP Power Amplifier at D-band (110-170 GHz) on this Interposer technology which was the first demonstration of an amplifier above 100 GHz on a Silicon Interposer (FIGURES 2 and 3). These transistors from Teledyne have ft and fmax of 350 and 650 GHz respectively making them better than their silicon counterparts for Sub-THz power generation and amplification. This work showed that it is possible to combine the best of both worlds – high performance III-V transistors with Waferscale Silicon packages.

In this PhD, the work described above will be continued to develop even more complex circuits combining III-V chiplets with IMEC’s RF Silicon interposer targeting Radar applications above 100 GHz.

During your PhD career at imec you will be embedded in a team with designers of active and passive RF and mm-wave circuits and components. You will also have access to imec’s world class R&D fab to realize your designs as well as tweak the underlying technology parameters. We also have a fully equipped RF Lab where you can perform different measurements to validate your designs.

References:

- H. Lin et. al., 91.5%-Efficiency Fully Integrated Voltage Regulator with 86fF/μm2-High-Density 2.5D MIM Capacitor, IEEE VLSI 2021

- X. Sun et. al., Cost-effective RF interposer platform on low-resistivity Si enabling heterogeneous integration opportunities, IEEE ECTC 2022

- R. Chen et. al., Backside PDN and 2.5D MIMCAP to Double Boost 2D and 3D ICs IR-Drop beyond 2nm Node, IEEE VLSI 2022

- S. Sinha et. al., Hetero-integration of InP Chiplets on a 300 mm RF Silicon Interposer for mm-wave Applications, IEEE IEDM 2024

- X. Sun et. al., RF Si interposer platform for chiplets based heterogenous systems, IEEE ECTC 2025

Required background: Master Degree in Electrical/Electronics/Telecommunication Engineering

Type of work: 70% modeling/simulation, 20% experimental, 10% literature

Supervisor: Nadine Collaert

Daily advisor: Siddhartha Sinha

The reference code for this position is 2026-112. Mention this reference code on your application form.