Early-Stage Thermal Screening Methodology for Advanced 3D HBM–GPU Integration

Master projects/internships - Leuven | More than two weeks ago

From early insight to informed system-level decisions

Context

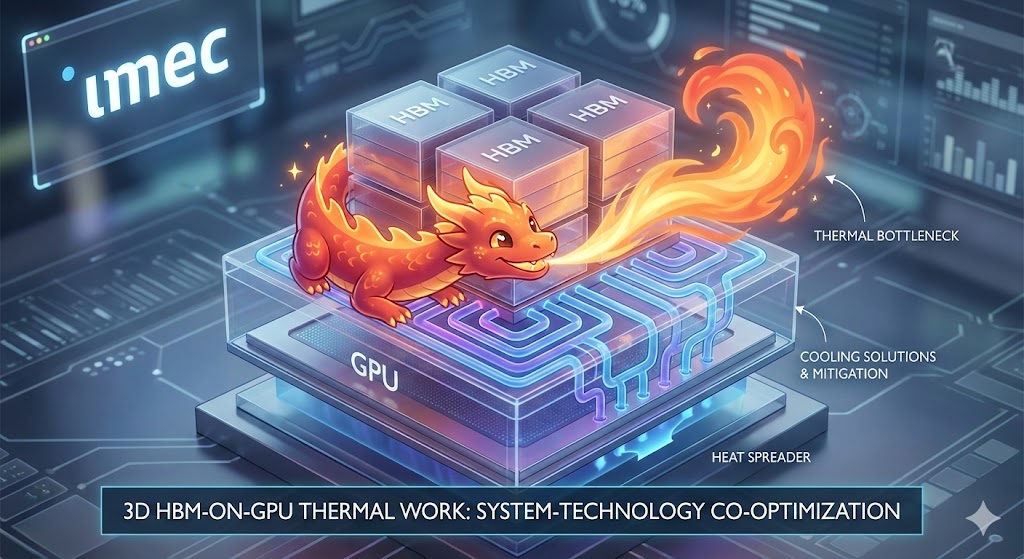

Advanced HBM–GPU integration is a key enabler for next-generation AI systems, yet thermal constraints remain a primary limiter. imec has recently demonstrated system-technology co-optimization approaches to mitigate thermal bottlenecks in advanced 3D HBM–on-GPU concepts under realistic power conditions[1].

However, early-stage design decisions are still often dominated by expensive, slow iteration cycles. There is a strong need for fast, data-driven screening methodologies that can translate power dissipation signatures into actionable guidance on which integration solutions should be prioritized for detailed analysis.

Objective

Develop a portable methodology and prototype toolchain that leverages power-map analytics to enable early-stage screening and prioritization of candidate advanced integration solutions. The internship focuses on building robust, architecture-consistent power-map descriptors and a scoring workflow that supports design-space exploration under limited information.

Key responsibilities

- Power-map processing pipeline (Python-first)

Build a reproducible pipeline to ingest, normalize, re-bin, and analyze workload-derived power maps; support multiple map formats and resolutions. - Feature engineering for power-map “fingerprints”

Define and implement multi-scale spatial descriptors capturing power concentration, heterogeneity, clustering behavior, and structural regularities in a way that is robust across workloads and mapping conventions. - Architecture-consistent synthetic power-map generation

Create synthetic power-map variants that remain consistent with computer-architecture realities, to stress-test methodology robustness and generalization. - Screening score and decision workflow

Propose a scoring framework that can rank candidate integration solutions using power-map fingerprints and limited configuration metadata, with emphasis on stability, interpretability, and sensitivity analysis. - Validation and reporting

Validate the screening workflow against a small set of reference cases and produce a concise report summarizing methodology, robustness, and recommended usage boundaries. - Optional stretch goal

Explore generative data augmentation (e.g., GAN-style synthesis) to enrich the space of architecture-consistent power maps for robustness testing (kept optional and scoped to feasibility).

Candidate profile

- MSc or early PhD student in Electrical/Computer Engineering, Computer Architecture, or related fields.

- Strong hands-on programming skills; Python required (NumPy/Pandas; bonus: SciPy/scikit-learn).

- Solid understanding of computer architecture and workload behavior (power distribution drivers, compute/memory interaction).

- Comfortable with building end-to-end research prototypes: data processing, metrics design, benchmarking, and clear documentation.

- Interest in thermal/power topics and advanced packaging is a plus, but the internship is primarily methodology- and tooling-driven.

What you will deliver

- A clean and reproducible Python toolchain for power-map analytics and screening.

- A documented set of power-map fingerprints and a screening score.

- A short technical report including robustness analysis and recommended best practices for using the methodology in early-stage exploration.

- A possible co-author publication with other team members, depends on the final delivery results.

Environment

You will work in imec’s highly interdisciplinary research environment, at the intersection of cross technology co-optimization (XTCO), power and thermal modeling, memory and architecture research, and EDA methodology development.

The internship is embedded in imec’s XTCO program[2], where architectural, physical, and system-level considerations are jointly explored to address next-generation compute challenges.

The work is hands-on and methodology-driven, with a strong emphasis on building reusable analysis pipelines rather than isolated simulations.

References

[1] https://www.imec-int.com/en/press/imec-mitigates-thermal-bottleneck-3d-hbm-gpu-architectures-using-system-technology-co

[2] https://www.imec-int.com/en/expertise/cmos-advanced-and-beyond/xtco

Type of Internship: Combination of internship and thesis

Master's degree: Master of Engineering Technology; Master of Science; Master of Engineering Science

Required educational background: Computer Science; Electrotechnics/Electrical Engineering

Duration: 6-12 months

For more information or application, please contact the supervising scientists Yukai Chen (yukai.chen@imec.be) and Matthew Walker (matthew.walker@imec-int.com).

Imec allowance will be provided for students studying at a non-Belgian university.