Cross-technology co-optimization (XTCO)

A holistic approach to system scaling, connecting AI workload challenges to technology innovations.

The recent history of semiconductor scaling shows a trend of broadening perspectives to drive innovation more purposefully:

- Design-technology co-optimization (DTCO) focused on circuit-level needs to guide technology innovations.

- System-technology co-optimization (STCO) took a wider view, identifying technology solutions that deliver system-level improvements.

Cross-technology optimization (XTCO) is imec's next step in holistic approaches to chip scaling, delivering system-level solutions that help accelerate product readiness.

XTCO aims to optimize complete systems, such as complex processor architectures, across all available chip technologies: CMOS logic, memory, 3D integration, optical interconnects, and more.

A holistic approach involving the full semiconductor ecosystem

Such a comprehensive approach to system scaling brings challenges that go beyond compute performance: thermal considerations, power distribution and power management, memory density and memory bandwidth, compute density, and compute fabric – the pillars of imec’s XTCO program.

Explore these pillars in more detail

Optimizing each pillar means identifying bottlenecks and exploring technologies to address them. This process must always include attention for potential repercussions elsewhere in the system.

The XTCO approach requires collaboration across the entire semiconductor ecosystem:

- Fabless and system companies

- Chip IP and EDA providers

- Device manufacturers, IDMs, and foundries

- Equipment and material suppliers

As the world’s leading independent semiconductor R&D hub, imec offers unique infrastructure and multidisciplinary expertise. It’s the ideal place for a precompetitive XTCO research program, enabling all ecosystem actors to engage in extensive dialogue about the future of system scaling.

XTCO to tackle the challenges posed by next-gen AI systems

One of the XTCO program’s main goals is to enable systems optimized for future compute demands. These demands stem from the explosive growth of AI, which presents a dual challenge:

- Energy efficiency: Many AI applications (such as large language models) depend on high-performance compute (HPC), which risks becoming unsustainable. With dimensional scaling slowing down, system-level innovations are needed to reduce energy per compute operation.

- Diversity of workloads: AI applications span HPC, mobile, edge, and more. Each requires tailored system architectures to achieve maximum efficiency.

The XTCO program tackles these issues by connecting AI workload challenges to semiconductor hardware innovations.

This enables fabless and system companies to bring their workload-driven challenges closer to technology development — and help steer innovation.

Pillars of imec’s XTCO program

The XTCO program builds on imec’s renowned core technology programs in logic, memory, 3D integration, and optical I/O. But the perspective is that of a system engineer, focused on system-scaling metrics rather than individual technologies. These metrics form the pillars of XTCO:

1. Compute density

Increasing operations per mm² directly boosts overall performance. Key contributors include:

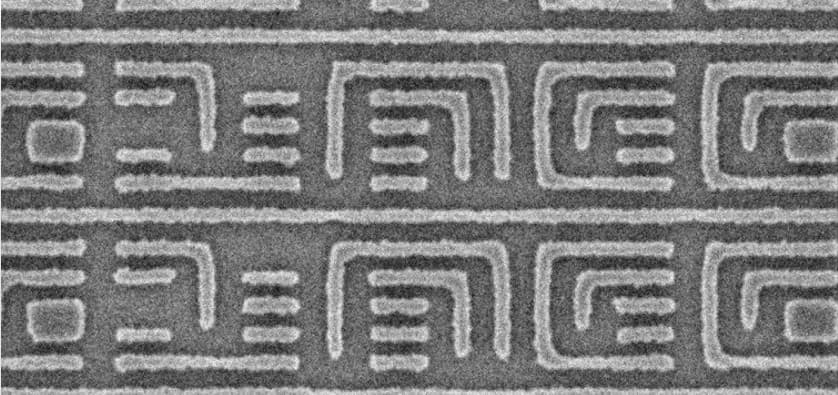

- Extension of the device scaling roadmap through CFET transistors (in tandem with BSPDN), patterning innovations such as a curvilinear approach, alternative channel materials, channel engineering for improved carrier mobility, and design-technology co-optimization (DTCO)

- Supply voltage (VDD) scaling

- Functional scaling of CMOS, known as CMOS 2.0

CMOS 2.0 leverages the third dimension to increase compute density.

2. Power delivery

With each new logic node, power density (W/mm²) increases. Improving power delivery efficiency can be achieved through:

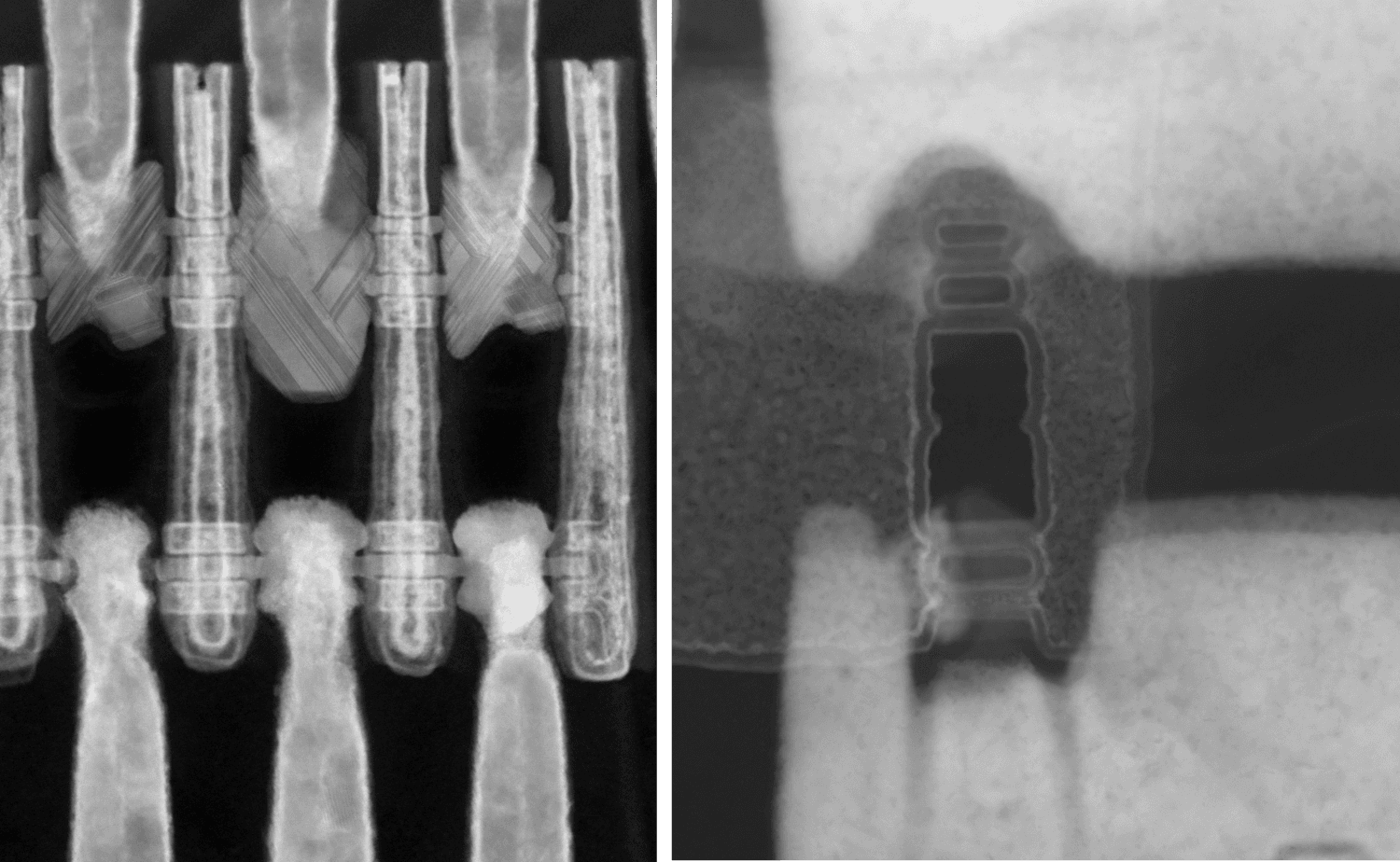

- 2.5 and 3D integration technologies

- new materials and components

- novel power management architectures and voltage conversion approaches

3. Thermal performance

Many systems are limited by their thermal performance: from AI GPUs struggling with excess heat from 3D stacking used to boost performance density, to mobile SoCs facing extreme hotspots from highly dynamic workloads.

The XTCO program identifies and addresses thermal issues using advanced simulation capabilities and test vehicles that capture the thermal behavior of packaged systems.

2025 press release: Imec mitigates thermal bottleneck in 3D HBM-on-GPU architectures

4. Memory density and bandwidth

Next-gen memory challenges go beyond storage capacity. Data transfer between memory and processors has become a bottleneck, with compute performance now outpacing memory bandwidth.

The XTCO program uses agile use cases to inform choices of technologies such as enhanced SRAM, scaled DRAM and high-bandwidth compute express link (CXL) processor-memory interfaces.

5. Compute fabric

This most recent pillar examines optical and electrical links, transceivers, and networking protocols that underpin system interconnects.

Join the XTCO program

The XTCO program is a unique opportunity to gain insights into how to confidently scale AI compute systems. It builds on imec’s ability to:

- Bring together all players in the semiconductor value chain.

- Shape and pioneer long-term technology roadmaps.

- Model and simulate system-level performance, backed by silicon data.

By joining the XTCO program, you can contribute to its roadmap and gain first access to results.

Click the contact button below to set up a meeting with our team.