[NanoIC topic] Exploring defect mechanisms and test strategies in next-generation Spin orbit torque (SOT)-MRAM

PhD - Leuven | More than two weeks ago

Magnetic random-access memory (MRAM), leveraging the spin properties of materials for data storage, is a non-volatile memory technology that has the potential to address the limitations of charge-based memory devices as we migrate towards advanced technology nodes and high-density applications. The key aspects of MRAM technology include its inherent non-volatility, low operating power, low read and write latencies, high endurance and low leakage. In recent years, MRAM technology has demonstrated significant advances in technology readiness, particularly with the spin transfer torque MRAM (STT-MRAM) variant. While STT-MRAM has indeed achieved commercialization as an embedded FLASH replacement memory in consumer electronics, it faces growing challenges in addressing the burgeoning high performance compute (HPC) needs owing to inherent trade-offs between fast switching speeds and long-term endurance, primarily attributed to the shared read and write current paths.

To address these challenges, spin orbit torque MRAM (SOT-MRAM) has emerged as a promising alternative by decoupling the read and write paths. This technology leverages spin-orbit torque (SOT) phenomenon, where a lateral charge current flowing through a heavy metal layer (e.g., tantalum (Ta), tungsten (W), or platinum (Pt)) underneath the magnetic tunnel junction (MTJ), generates a spin torque responsible for magnetization reversal. The physics responsible for SOT-driven switching enables ultra-fast deterministic writes at speeds up to 5 GHz, while also demonstrating a projected reliability of up to 1015 cycles at 1 ns write speeds [1]. More importantly, the separation of read and write paths mitigates the reliability issues seen in STT-MRAM [2]. These properties allow SOT-MRAMs to be useful in a variety of applications such as Internet-of-Things (IoT), AI accelerators and edge AI, automotive, aerospace, and data centers and high performance computing.

Manufacturing processes of integrated circuits (ICs), including those based on SOT-MRAM devices, usually involve several fabrication steps that require high precision, and hence are also ‘defect’-prone. Defects can be classified as global (occurring over the entire wafer; due to mask misalignment, for example) or local ‘spot’ (dust on IC, material stack imperfections, etc) defects. Because spot defects might occur as a ‘lone wolf’ at virtually any place in the IC, detecting them can be compared to searching for the proverbial “needle-in-the-haystack”. Defect creation during fabrication can result in reduced wafer yield and poor device performance, amongst others. Hence, it is important to identify the sources of such defects by developing appropriate defect models, fault primitives, test algorithms and routines.

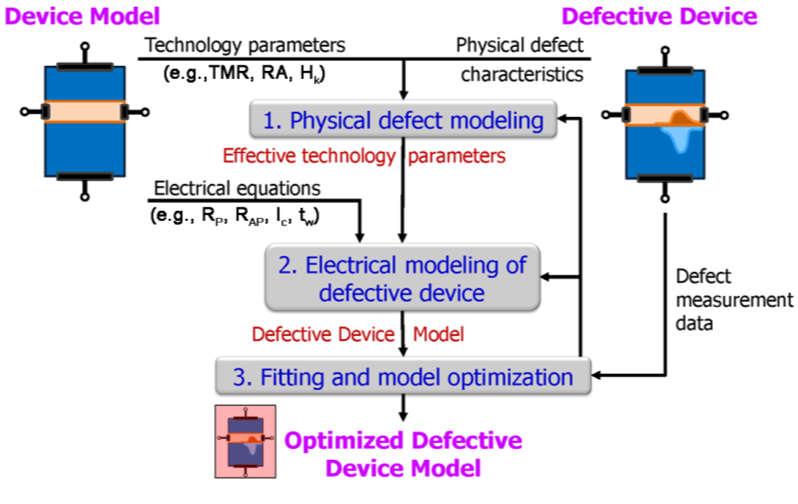

This PhD will focus on the study of defects in SOT-MRAM devices fabricated in IMEC’s state-of-the-art 300mm pilot line. Conventional research has modelled defects in SOT-MRAM devices as linear resistors, but this has resulted in creation of defect models for non-existent defects, and thus poor fault-testing routines. Thus, there is a need to understand the fundamental mechanisms of SOT-MRAM devices and its unique failure mechanisms to develop device-aware test (DAT) routines [3, 4]. DAT has been successfully applied to STT-MRAMs of IMEC [5,6].

This PhD research will focus on the following tasks -

- Experimental characterization and identification of failure mechanisms in SOT-MRAMs

- Modelling identified defects using accurate physics- and spice-based models

- Analyzing the impact of the defect on the functional behavior of the memory

- Development of a defect-parametrized behavioural model for SOT-MRAM, and

- Test solutions and design-for-testability (DfT) circuits for SOT-MRAM technology.

- You will be part of a collective effort: strong interaction with device technology engineers and other modelling experts is expected and encouraged

In the first phase, the student will perform extensive literature search on the existing methodologies of defect identification, modelling and test solution development, specifically for SOT-MRAM technology. The student is expected to understand and assimilate the shortcomings of the conventional methods, and the need for a device-aware approach. In parallel, the student will be expected to learn and develop software routines (Python or Matlab) for data post-processing and modelling activities. With the in-depth knowledge gained, the following phases will involve the tasks detailed above.

References

- V. D. Nguyen, S. Rao, K. Wostyn, S. Couet, ‘’Recent progress in spin-orbit torque magnetic random-access memory’’, npj Spintronics, 2 (48), 2024, https://doi.org/10.1038/s44306-024-00044-1

- Dieny, B. et al. Opportunities and challenges for spintronics in the microelectronics industry. Nat. Electron. 3, 446 (2020).

- Lizhou Wu, Mottaqiallah Taouil, Siddharth Rao, Erik Jan Marinissen, Said Hamdioui, “Electrical Modeling of STT-MRAM Defects”, in Proceedings 2018 IEEE International Test Conference (ITC), Phoenix, AZ, USA, October 2018, pp. 1–10, doi:10.1109/TEST.2018.8624749

- Moritz Fieback, Lizhou Wu, Guilherme Cardoso Medeiros, Hassen Aziza, Siddharth Rao, Erik Jan Marinissen, Mottaqiallah Taouil, Said Hamdioui, “Device-Aware Test: A New Test Approach Towards DPPB Level”, IEEE International Test Conference (ITC), 2019, pp. 1-10.

- Lizhou Wu, Siddharth Rao, Mottaqiallah Taouil, Guilherme Cardoso Medeiros, Moritz Fieback, Erik Jan Marinissen, Said Hamdioui, “Defect and Fault Modeling Framework for STT-MRAM Testing”, in IEEE Transactions on Emerging Topics in Computing, pp. 1–1, December 2019, doi:10.1109/TETC.2019.2960375

- Sicong Yuan, Mottaqiallah Taouil, Moritz Fieback, Hanzhi Xun, Erik Jan Marinissen, Gouri Sankar Kar, Sidharth Rao, Sebastien Couet, Said Hamdioui, “Device-Aware Test for Back-Hopping Defects in STT-MRAMs”, Design Automation and Test in Europe, 2023, pp. 1-6.

Required background: Electrical Engineering, Computer Science, Engineering Science

Type of work: 10% literature study, 40% modeling, 40% experimental analysis, 10% reporting in meetings, conferences, technical notes and journals

Supervisor: Said Hamdioui

Co-supervisor: Siddharth Rao

Daily advisor: Siddharth Rao

The reference code for this position is 2026-006. Mention this reference code on your application form.