CMOS: advanced and beyond

Discover why imec is the premier R&D center for advanced logic & memory devices.

Integrated photonics

Take a look at technologies for optical transceivers, sensors and more.

Health technologies

See how imec brings the power of chip technology to the world of healthcare.

Sensing and actuation

Explore imec’s CMOS- and photonics-based sensing and actuation systems.

Connectivity technology

Look into our reliable, high-performance, low-power network technologies.

More expertises

Discover all our expertises.

Research

Be the first to reap the benefits of imec’s research by joining one of our programs or starting an exclusive bilateral collaboration.

Manufacturing

Go from idea to scalable and reliable semiconductor manufacturing with IC-Link.

Venturing and startups

Kick-start your business. Launch or expand your tech company by drawing on the funds and knowhow of imec’s ecosystem of tailored venturing support.

Education and workforce development

Imec supports formal and on-the-job training for a range of careers in semiconductors.

NanoIC pilot line

Aligned with the EU Chips Act, access to the pilot line will accelerate beyond-2nm innovation.

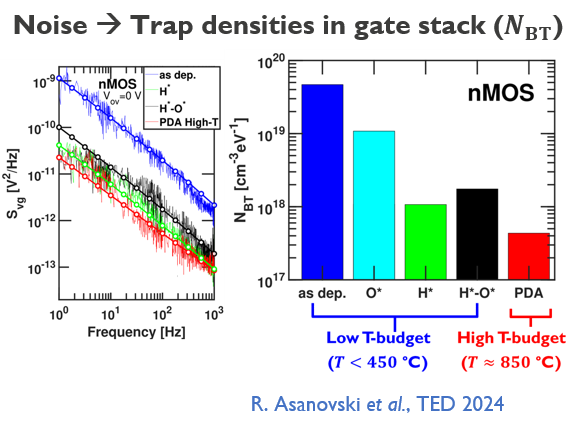

[NanoIC topic] Reliability characterization of advanced CMOS nodes with low-frequency noise

PhD - Leuven | More than two weeks ago

Turning device noise into insight for future CMOS reliability.

Advanced CMOS nodes, such as nanosheet-based transistors, introduce new architectural complexities that challenge conventional reliability evaluation methods. Moreover, physical degradation mechanisms become harder to detect and predict using standard techniques as devices scale down. This PhD project investigates low-frequency noise as a non-destructive and sensitive tool to assess reliability in these emerging technologies. The research aims to establish a fundamental link between noise behavior and key failure mechanisms, including bias-temperature instability (BTI) and time-dependent dielectric breakdown (TDDB). Through experimental characterization and physics-based modeling, the project will develop new methodologies and knowledge to support reliability screening and robust design of future CMOS technologies. The outcomes will contribute to improving the fundamental understanding of reliability in nanoscale devices and enable more efficient development of next-generation integrated circuits.

Required background: Electrical Engineering or equivalent

Type of work: 60% experimental, 30% modeling/simulation, 10% literature

Supervisor: Kristof Croes

Daily advisor: Ruben Asanovski

The reference code for this position is 2026-029. Mention this reference code on your application form.