Thermo-Mechanical Reliability for Advanced Microelectronics packaging

PhD - Leuven | More than two weeks ago

Context

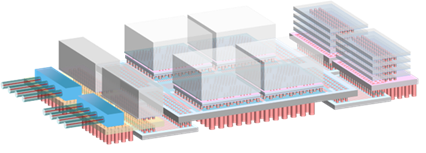

Redistribution layers (RDL) play an important role in advanced packaging technologies for integrated circuits (IC). The primary objective of the RDL is to redistribute the input/output (I/O) pads of a chip to a different layout or pitch, allowing for efficient and compact interconnections with other chiplets or package-level interconnects. The interconnects made of metal, like copper, are embedded in a dielectric, which acts as insulation between the metal traces and provides mechanical support. The chiplets are small, modular chips designed to perform specific function, such as CPUs or GPUs, and can be assembled into complete systems.

As electronic packages integrate diverse materials with varying coefficients of thermal expansion (CTE), thermal cycling during fabrication and operation induces mechanical stresses. These stresses can lead to reliability issues such as delamination, cracking, voiding, and fatigue.

This PhD research will focus on the thermo-mechanical reliability of advanced microelectronic packages, addressing both material-level behavior and system-level design strategies. The candidate will develop finite element (FE) or analytical models to predict stress and failure mechanisms, and will conduct experimental testing to calibrate and validate these models. The study will also investigate process and design strategies to mitigate stresses and enhance chiplets reliability.

Key Objectives

- Mechanical material’s characterization

- Thermal-mechanical analysis of the stress buildup due to CTE mismatch of the materials.

- Explore process and design strategies for stress mitigation and enhanced reliability of chiplets.

Candidate Profile

This position is ideal for candidates with a background in mechanical engineering, materials science, physics, or related fields. A strong interest in numerical modeling and experimental techniques is essential. Experience with finite element modeling (FEM) tools such as Ansys, Abaqus, or MSC Marc is highly desirable. Enthusiasm for multidisciplinary research in semiconductor technology is a must.

References

- Chiplet Interconnect Technology: Piecing Together the Next Generation of Chips: 3D In-Depth, Processes and Technology, Jul 03, 2024, Eric Beyne https://www.3dincites.com/2024/07/chiplet-interconnect-technology-piecing-together-the-next-generation-of-chips/

- A new approach to fan-out wafer-level packaging, https://www.imec-int.com/en/imec-magazine/imec-magazine-june-2019/a-new-approach-to-fan-out-wafer-level-packaging

- AMD CHIPLET ECOSYSTEM, WHITEPAPER | DECEMBER 09, 2024 https://www.amd.com/content/dam/amd/en/documents/solutions/technologies/chiplet-architecture-white-paper.pdf

- HETEROGENEOUS INTEGRATION – CHIPLETS, GLOBAL SEMICONDUCTOR ALLIANCE INTELLECTUAL PROPERTY INTEREST GROUP, February 2023 https://www.gsaglobal.org/wp-content/uploads/2023/02/2022-IPIG-Heterogenous-Integration-Chiplets-White-Paper-Final-v4.pdf

- The Role of Redistribution Layers (RDL) in Advanced Packages, Blogs, Interconnectology 101, Jul 09, 2025 · By Jillian McNichol https://www.3dincites.com/2025/07/the-role-of-redistribution-layers-rdl-in-advanced-packages/

Required background: Mechanical engineering, materials science, physics, or equivalent

Type of work: ~50% simulations, ~40% experimental, ~10% literature and technological study.

Supervisor: Houman Zahedmanesh

Co-supervisor: Mario Gonzalez

Daily advisor: Abdellah Salahouelhadj

The reference code for this position is 2026-085. Mention this reference code on your application form.