PhD position in microfluidics; Study of capillary underfill process for packaging optical interconnects into HPC & AI compute systems

PhD - Leuven | More than two weeks ago

Are you passionate about advancing the future of AI and high-performance computing (HPC)? Do you thrive in hands-on research environments and enjoy tackling complex physical challenges? Imec invites motivated candidates to apply for a PhD position focused on microfluidics and advanced packaging for next-generation computing systems.

Project Overview

Modern AI and HPC architectures are rapidly evolving, with chiplet-based designs driving innovation in advanced packaging technologies [1, 2]. As these systems push the boundaries of bandwidth and integration, optical communication—enabled by silicon photonics and integration techniques such as co-packaged optics—has become essential for connecting memory, processors, and peripheral components [3-7]. The reliability and performance of these optical interconnects depend on precise packaging processes, particularly the quality of the optical underfill that serves as an interface between photonic components.

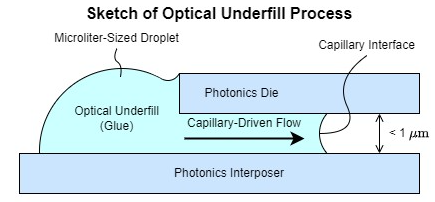

The optical underfill process involves drawing an epoxy-based resin through micron or sub-micron gaps between mating photonics dies using capillary forces. This seemingly simple step is complicated due to the complex rheological and wetting behavior of underfill materials at such small scales. Challenges such as void formation (entrapped air pockets) and poorly controlled gap heights can significantly impact device performance and long-term reliability. Accurate modelling and prediction of the underfill process are therefore critical for improving the process.

Research Objectives

As a PhD researcher, you will explore the capillary-driven behavior of complex fluids in sub-micrometer gaps, focusing on the following objectives:

- Characterize rheological and wetting properties of underfill materials within confined geometries.

- Apply experimental microfluidics techniques and optical-based characterization methods to study fluid behavior and defect formation.

- Develop advanced data analysis approaches to understand capillary filling in gaps with non-uniform heights.

- Create predictive models to describe and optimize the underfill process for next-generation packaging.

Candidate Profile

We are seeking highly motivated individuals with strong analytical skills, curiosity for complex physical systems, and a passion for scientific discovery. Ideal candidates will be eager to develop hands-on expertise in experimental fluid characterization and possess (or be willing to learn) computational fluid dynamics (CFD) or related modelling techniques.

Key qualifications:

- Background in physics, materials science, engineering, or a related field.

- Interest in fluid mechanics, wetting phenomena, and advanced packaging.

- Experience with experimental techniques and/or computational modelling is a plus.

Why Join imec?

At imec, you will become part of a diverse, collaborative, and high-energy research community at the forefront of semiconductor and photonic integration. Working alongside experts from multiple disciplines, you will gain practical experience in fluid mechanics, materials science, and advanced packaging technologies. This PhD position offers a unique opportunity to contribute to next-generation AI/HPC hardware and build a career in a world-leading research hub.

Ready to shape the future of computing? Apply now and join us in driving innovation at the intersection of microfluidics, photonics, and advanced packaging.

References

- "The three-dimensional stacking of ICs is one way to further extend IC scaling. Imec explores different paths for such 3D integration.". imec, Retrieved September 12, 2025.

- "3DFabric". TSMC, Retrieved September 12, 2025.

- "Integrated photonics", imec, Retrieved September 12, 2025.

- "Advanced Packaging Evolution: Chiplet And Silicon Photonics-CPO". Semiconductor Engineering, Retrieved September 12, 2025.

- Mahajan, Ravi, et al., “Co-Packaged Photonics For High Performance Computing: Status, Challenges And Opportunities”, Journal of Lightwave Technology (2022), https://doi.org/10.1109/JLT.2021.3104725.

- Marchetti, Riccardo, Lacava, Cosimo, Carroll, Lee, Gradkowski, Kamil, Minzioni, Paolo, “Coupling strategies for silicon photonics integrated chips”, Photonics Research (2019), https://doi.org/10.1364/PRJ.7.000201.

- Li, Yuan, Louri, Ahmed, Karanth, Avinash, “Scaling Deep-Learning Inference with Chiplet-based Architecture and Photonic Interconnects”, 58th ACM/IEEE Design Automation Conference (2021), https://doi.org/10.1109/DAC18074.2021.9586311.

Required background: Engineering, Science, Physics

Type of work: 45% modeling, 45% experimental, 10% literature

Supervisor: Geert Van Steenberge

Co-supervisor: Ben Jones

Daily advisor: Naghmeh Fatemi

The reference code for this position is 2026-180. Mention this reference code on your application form.