Active memory

To increase the performance and control the energy consumption of computer systems, various forms of active memory are crucial. This is how imec tackles their challenges.

In the area of active memory, a major challenge is to eventually tear down the memory wall, the delay between the time the CPU needs data from SRAM-based caches or DRAM, and the moment it can access it.

Pressing questions are:

- What are the bottlenecks that limit speed and how can we remove them?

- How can we improve the bandwidth and data protocols that are used to fetch the data?

- How do we ensure that memory remains coherent when multiple CPU cores access a shared cache?

Imec’s scientists tackle these challenges, amongst others, through system-level simulations. This allows to gain insight into the bottlenecks, to evaluate novel memories and see how they perform for various workloads.

Exploring MRAM

To eventually replace the levels of traditional SRAM-based caches, we are studying various kinds of magnetic random-access memories (MRAM). Each of these may help us overcome the memory bottleneck by improving speed, power consumption and/or memory density. But each also comes with its own benefits and challenges.

To further improve the density, our engineers are also actively researching selector devices that can be integrated with the magnetic tunnel junctions, which are at the heart of these MRAM devices.

One level up in active memory: DRAM

When it comes to dynamic random-access memories (DRAM), dimensional scaling is also slowing down. Imec explores two possible paths to push DRAM technology to its ultimate limit and to help tackle the memory wall. These paths each have their own different technology, and each will call for new architecture standards to enable the next DRAM memory.

The first path is to improve the dynamic nature of the DRAM bit cells. With FeCapacitors, for example, that let DRAM bit cells store their charge for longer periods. These could markedly improve the retention time of the DRAM memory and introduce many other benefits:

- negligible refresh overhead

- fast switching to and from power down

- lower standby power

- possibility to push scaling a little bit further

Within its ferroelectric program, imec is developing ferroelectric-based metal-insulator-metal (MIM) capacitors to explore this path.

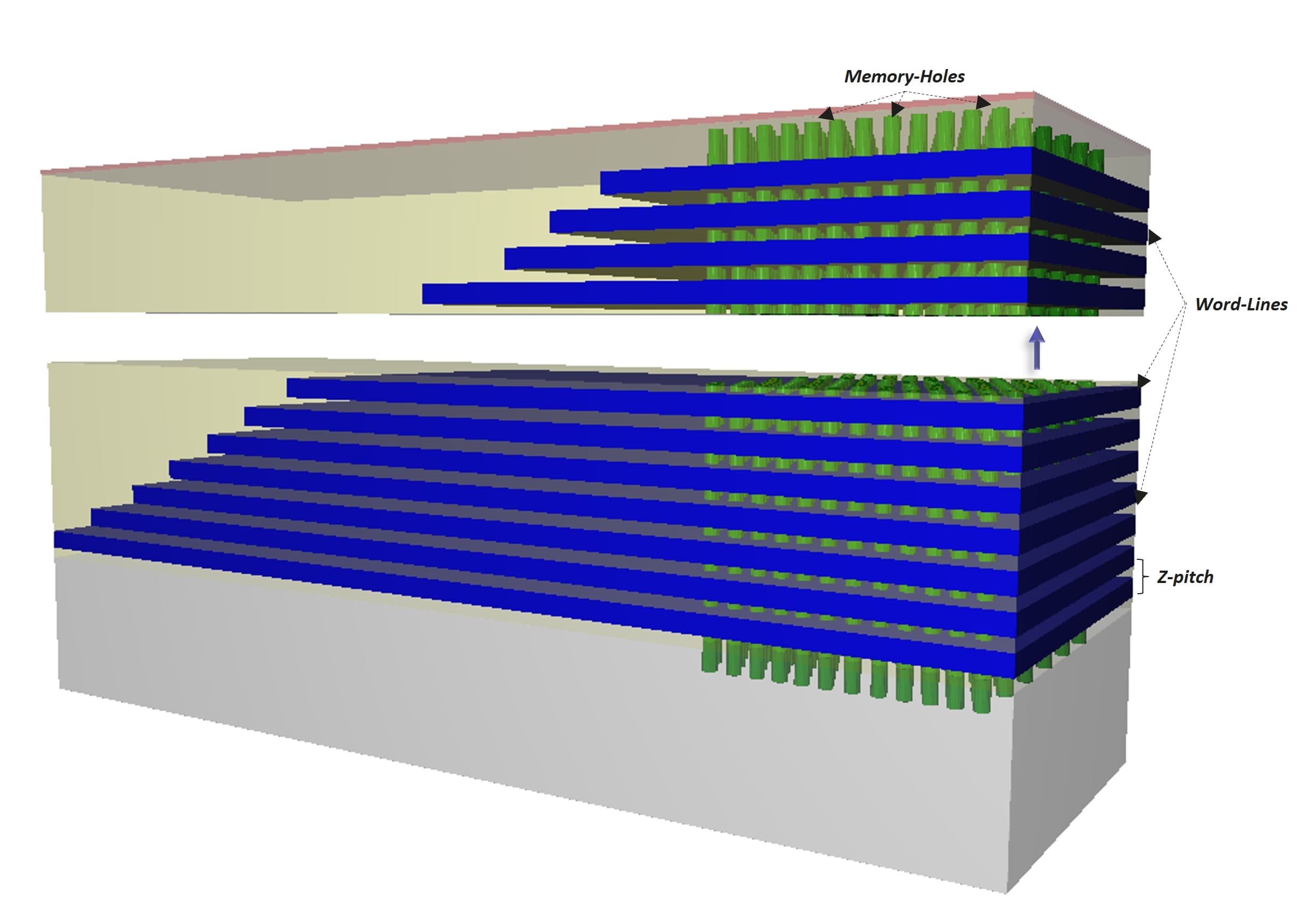

Imec also explores EUV lithography for patterning critical DRAM structures. As a more disruptive development, our scientists are working to enable 3D DRAM: cells are stacked on top of one another and peripheral circuits go underneath the array.

One option is to replace Si-based transistor within the DRAM cell with a thin-film IGZO transistor (indium-gallium-zinc-oxide). The high bandgap of this material ensures a low off-current, a characteristic that is mandatory for a DRAM cell transistor. Since we do not need silicon anymore to make the cell transistors, we can now move the periphery of the DRAM cell under the DRAM array. This way, the footprint of the memory cell can be significantly reduced.

2025 research update: a novel 3D buffer memory for AI and machine learning

2025 technology review: Disrupting the DRAM roadmap with capacitor-less IGZO-DRAM technology

2025 article: A technology platform for thermally stable DRAM peripheral transistors

The semiconductor industry has been looking to fill the gap between DRAM and NAND Flash in traditional high-performance computing system architectures. Imec researchers are exploring a promising avenue towards this goal: the potential of OTS-only memories for CXL applications.

The promise of OTS-only memories for next-gen compute system architectures

Want to more about our research or get involved?