Advanced Modeling of Ferroelectric Thin Films and Capacitors for Nonvolatile AI Memories

PhD - Leuven | More than two weeks ago

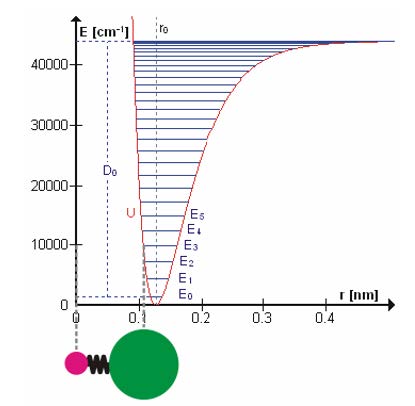

Ferroelectric (FE) materials are dielectrics with spontaneous polarization that can be electrically switched by an applied field, resulting in a switchable polarization. The discovery of CMOS-compatible, Hf-based ferroelectric thin films in 2010s has paved the way for a promising material platform for low-power, high-density, Back-End-of-Line (BEOL)-compatible memories. A notable example is the FeRAM (Ferroelectric Random Access Memory) based on FE capacitors, which is often seen as a promising candidate for memory-bound applications like AI [1].

One particularly interesting concept in FeRAM technology in the past years is the non-destructive readout (NDRO) operation [2] , where the readout only probes the capacitance difference between two polarization states without having to switch the dipoles, virtually allowing quasi-infinite read endurance. This makes it immensely relevant to AI inferencing where the workloads involve predominantly read operations that entail high read endurance. In the meantime, the understanding and modeling of NDRO however, have been far from conclusive, which has inevitably hindered physics-based predictive circuit- and system-design explorations. One major drawback of existing models such as [3] is that only quasi-static, small-signal capacitance is considered, whereas the actual FeRAM readout in circuits is by nature transient (i.e., large-signal), a regime in which NDRO dynamics are essential. Non-quasi-static modeling approaches including anharmonicity (i.e., subharmonics and harmonics generation) have been recently suggested [4] that indicate qualitatively similar trends to experimental observations, yet the exact mechanics has yet to be investigated and validated against experimental data.

Another latest development of FeRAM is the co-integration of other BEOL-compatible materials, notably oxide semiconductor (OSC) electrodes such as IGZO (InGaZnO) [5] that, in NDRO, provides additional capacitive memory window enhancement. The use of OSC electrodes in FeRAM nevertheless introduces carrier accumulation/depletion and possible secondary effects such as tunneling/field emission/etc. [6] – all of which need to be thoroughly understood and evaluated for device design and optimization. In addition, a different type of FE memory device at the forefront of AI memory research, the OSC-channel FeFET shares a stack structure with the OSC-FeRAMs [6] . An increased understanding of this OSC-Fe stack would lend insights into the design and operation of both devices.

This thesis seeks to establish a modeling framework to elucidate the capacitive response of FE thin films and capacitors, and as such to provide predicative guidelines for the design and operation of FE-based AI memories. This could include (but is not limited to): developing self-consistent FeCAP models for read and write, investigating temperature-dependent variability and stochasticity, exploring optimal device operating biases/timing schemes, etc. To support modeling effort, the student will perform hands-on experimental measurements on FeCAPs fabricated at imec on 300 mm Si wafers. The resulting fundamental models will be used to benchmark and optimize the design of individual FeCAPs and full memory arrays. These learnings will be further transferred to other FE-based devices (e.g., FeFETs) for guiding/gauging their application-specific power/area/reliability metrics.

What will you do?

- Performing electrical characterization on automatic / semi-automatic / manual measurement setups

- Numerical modeling of FE-thin films / capacitors, either using commercial TCAD tools, or by developing customized solvers

- Abstracting the numerical modeling findings into compact, circuit-compatible models of FE memory devices and extracting basic circuit figures of merits (read latency, sensing margin, read/write disturb, error rate, etc.)

- Performing Design-Technology Co-Optimization to assess the scalability (power-performance-area-cost) of different possible FE memory technologies

Who are you?

- Holding a Master's degree in Electrical Engineering / (Applied) Physics / Nanotechnology / Materials Science

- Having a strong analytical mindset plus enthusiasm for critical thinking

- Having excellent knowledge of solid-state physics, preferably with a good command of materials science

- Open to engaging in both hands-on lab work and coding

References:

- A. Lu, J. Lee, T.H. Kim et al., "High-speed emerging memories for AI hardware accelerators," in Nat. Rev. Electr. Eng., vol. 1, pp. 24–34, 2024.

- Y. -C. Luo et al., "Experimental Demonstration of Non-volatile Capacitive Crossbar Array for In-memory Computing," 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2021.

- Y. Xiang et al., "Compact Modeling and Design Exploration of Non-Destructive Read-Out 1T1C FeRAM," in IEEE Trans. Elec. Dev., 71(8), pp. 4685-4691, 2024.

- S. Mukherjee et al., "Fundamental Insight into Non-linear Dielectric Response in Ferroelectric Capacitors to Understand and Improve the Capacitive Memory Window for Non-destructive Read," as discussed at the 55th IEEE Semiconductor Interface Specialists Conference (SISC), San Diego, Dec. 2024.

- S. Mukherjee et al., "Improved Capacitive Memory Window for Non-Destructive Read in HZO-Based Ferroelectric Capacitors with Incorporation of Semiconducting IGZO," 2024 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2024.

- Z. Chen et al., "Understanding the Slow Erase Operation in IGZO-Channel FeFETs: The Role of Positive Charge Generation Kinetics," in IEEE J. Elec. Dev. Soc., 13, pp. 245-251, 2025.

Required background: Electrical Engineering, (Applied) Physics, Nanotechnology, Materials Science or proven equivalent

Type of work: 60% modeling, 30% characterization, 10% literature

Supervisor: Maarten Rosmeulen

Co-supervisor: Jan Van Houdt

Daily advisor: Yang Xiang, Nicolo Ronchi

The reference code for this position is 2026-003. Mention this reference code on your application form.