Machine Learning-Driven Modeling and Design of Next-Generation 3-D NAND Flash Memory Architectures

PhD - Leuven | More than two weeks ago

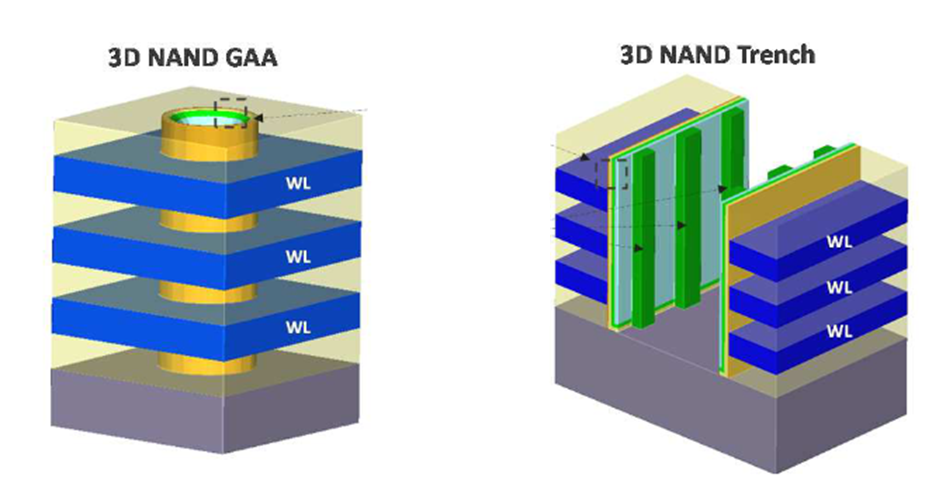

Memories are a fundamental component of all electronic systems. Non-volatile data storage is at the forefront of the electronics industry, representing over 80% of all transistors produced. Three-dimensional (3-D) NAND flash memory is the predominant non-volatile technology, being integrated into a broad array of applications, like mobile phones, personal computers, data centers, and artificial intelligence systems. Memory densities are continuously advancing; cutting-edge 3-D NAND flash technologies have achieved bit densities of 20 Gigabit per mm², with projections estimating 256 Gb/mm² by 2028. These high densities are obtained through vertically arranged cells that capture charge in a SiN layer [1].

The typical way of scaling bit densities by adding more cells on a vertical string is expected to slow down as the etch required to create the string hole becomes more challenging. This means there is a need for new, innovative cell designs that go beyond the standard structures of today, which are in essence still 2-D cells stacked in the vertical direction. These novel designs could make full use of the 3-D nature of the string to achieve denser stacking, while maintaining good memory operation. Additionally, co-designing the cells with the array architecture would open up new possibilities that are currently unexplored.

As the space of possible cell and array configurations is huge, finding an optimal design will require algorithmic optimization. Machine learning based algorithms like Bayesian optimization have recently been used successfully to optimize transistor designs for logic and power applications [2]. So far, this approach has not yet been tried on memory cells or array configurations.

As a PhD researcher in this topic, you will first perform a literature review to become familiar with the current state-of-the-art in 3-D NAND modeling and cell designs. Next, you will get acquainted with the in-house simulation software and commercial TCAD software. Once you achieve a deep understanding of the operation and scaling limits of current flash cells, you will start your exploration of new designs. These new concepts might require modification of the modeling approach. After a design and modeling flow is set up, machine learning based optimization tools can be employed to search a wider parameter space that connects cell and array level.

Ultimately, this PhD topic has the potential to impact devices that people worldwide use every day. It offers a combination of computational modeling and simulation with device and array architecture design. You will be embedded within the storage memory team at imec, which performs world-leading research on advanced flash cells. You will interact frequently with both modeling and integration experts, ensuring that your work remains relevant for practical implementation in future products. You will be able to rely on an extensive set of existing modeling tools and expertise to get you started in your research project.

[1] S.S Kim et al. "Review of semiconductor flash memory devices for material and process issues." Advanced Materials, vol. 35. 43, 2200659, 2023.

[2] P. -J. Chuang, et al., "Algorithmic Optimization of Transistors Applied to Silicon LDMOS," IEEE Access, vol. 11, pp. 64160-64169, 2023.

Required background: Nanoelectronics, semiconductor device modeling, computer science

Type of work: 45% modeling and implementation, 45% design, 10% literature

Supervisor: Maarten Rosmeulen

Daily advisor: Devin Verreck

The reference code for this position is 2026-002. Mention this reference code on your application form.