Environment for system-technology co-optimization exploration

If we want to continue on the path of life improvements through digitization, we can no longer put our faith in a single semiconductor roadmap. We need to explore new combinations of technology and systems. And imec USA is one of the places to do so.

Is Moore’s law dead? Maybe. It certainly is changing its nature. The march forward will continue, but the idea of one predictable roadmap for semiconductor development has been overtaken by the reality of diversification. There are now separate roadmaps for memory and logic, low-power and high-performance, sensors, integration and so on.

In the future, optimized technologies will become the norm for every part of the digital ecosystem: from ultra-low power cognitive edge devices to ultra-performing cloud servers. Making it possible for our devices to keep up with our demands ... and creating possibilities we never even thought of.

Clean slate

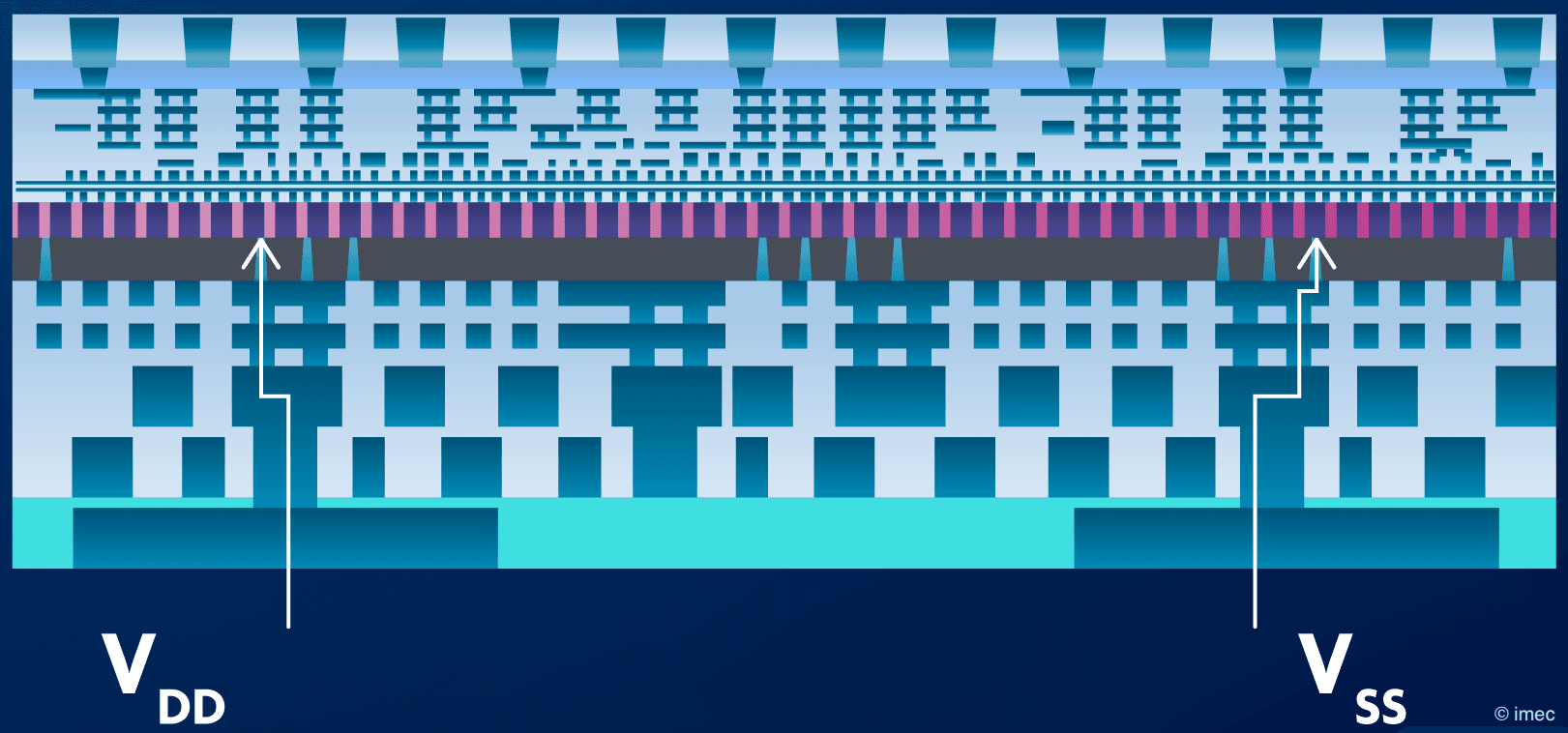

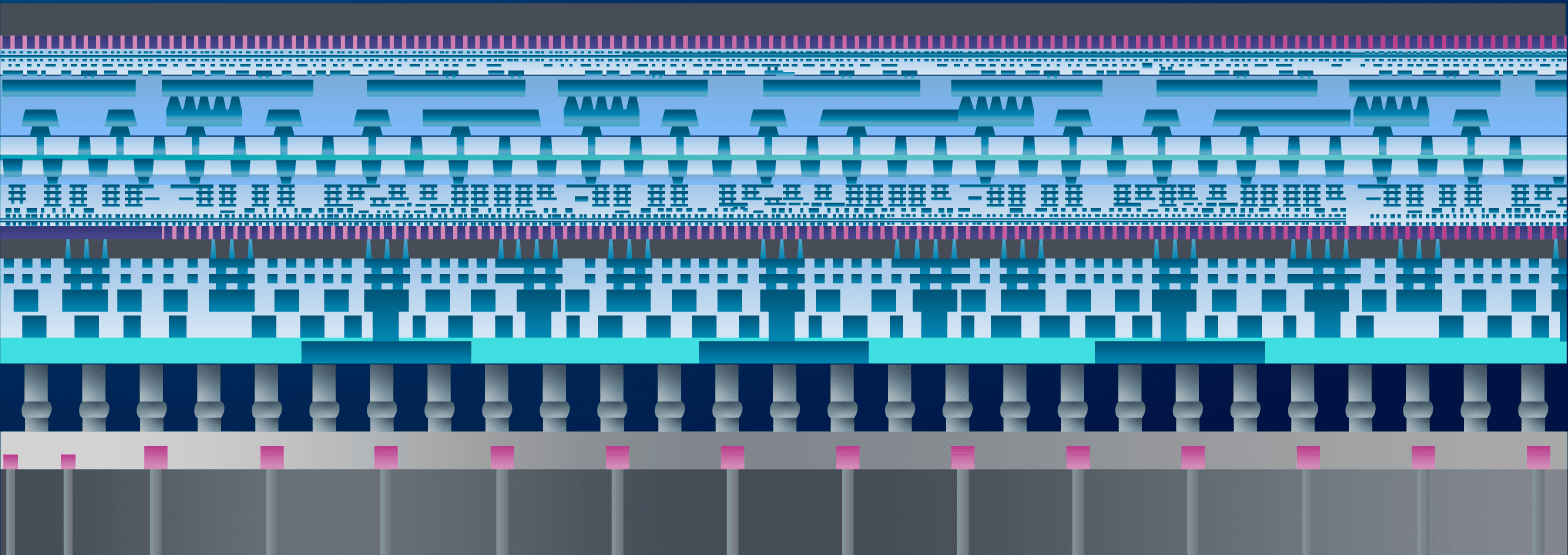

System-technology co-optimization starts with the disintegration of our existing system-on-chips. After designing and processing the subsystems separately, they are re-integrated using state-of-the-art 3D integration technologies.

It’s a process that involves a rare combination of technology and design expertise. And which can be approached in two ways:

- top-down – The needs of the targeted application dictate the technologies and the system design.

- bottom-up – New system-technology configurations suggest new or improved applications.

Room for experiment

Because of its inherent explorative nature, system-technology co-optimization needs an environment where researchers can

- build accurate technology models

- put them together

- link that outcome to the application level by making what-if analyses

For instance: what if we put the memory on top of the logic system? Would that make machine learning more efficient? Or vice versa: if we want to enhance our AR/VR experiences, what sort of system-technology combination do we need?

One of the goals of the imec USA is to provide such an exploration environment – by combining the deep technology knowhow from imec with the wealth of system application knowhow that we find in the US.